# LINEAR APPLICATIONS

| , |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

# NATIONAL LINEAR APPLICATIONS HANDBOOK

January 1972

#### **PREFACE**

The purpose of this handbook is to provide a fully indexed and cross-referenced collection of linear integrated circuit applications using both monolithic and hybrid circuits from National Semiconductor.

Individual application notes are normally written to explain the operation and use of one particular device or to detail various methods of accomplishing a given function. The organization of this handbook takes advantage of this innate coherence by keeping each application note intact, arranging them in numerical order, and providing a detailed Subject Index composed of approximately 1000 references to the main body of the text. This Subject Index provides the key to efficient access to the applications experience accumulated over the last five years by National Semiconductor.

### APPLICATION LITERATURE NUMERICAL LIST

| APPLICAT       | ON NOTES                                                   | DATE         |

|----------------|------------------------------------------------------------|--------------|

| AN-1           | A Versatile Monolithic Voltage Regulator                   | 11/67        |

| AN-2           | Designing Switching Regulators                             | 3/69         |

| AN-3           | Drift Compensation Techniques for Integrated DC Amplifiers | 11/67        |

| AN-4           | Monolithic Op Amp — The Universal Linear Component         | 4/68         |

| AN-5           | A Fast Integrated Voltage Follower with Low Input Current  | 5/68         |

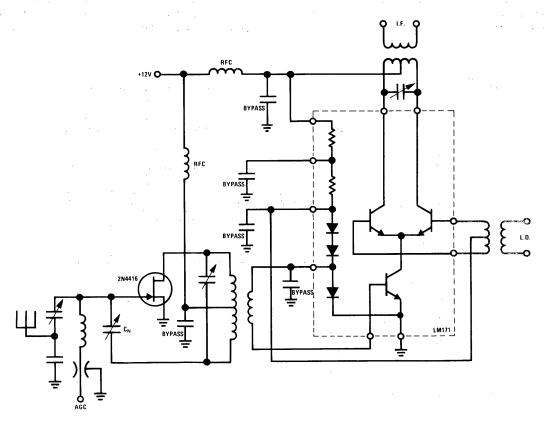

| AN-6           | Tuned Circuit Design Using Monolithic RF/IF Amplifiers     | 3/68         |

| AN-8           | New Uses for the LM100 Regulator                           | 6/68         |

| AN-10          | Low Power Operational NH0001 Amplifier                     | 12/68        |

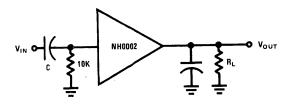

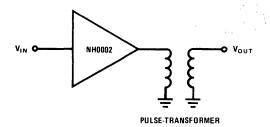

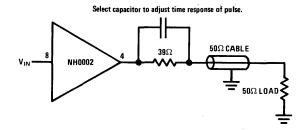

| AN-13          | NH0002 Current Amplifier                                   | 9/68         |

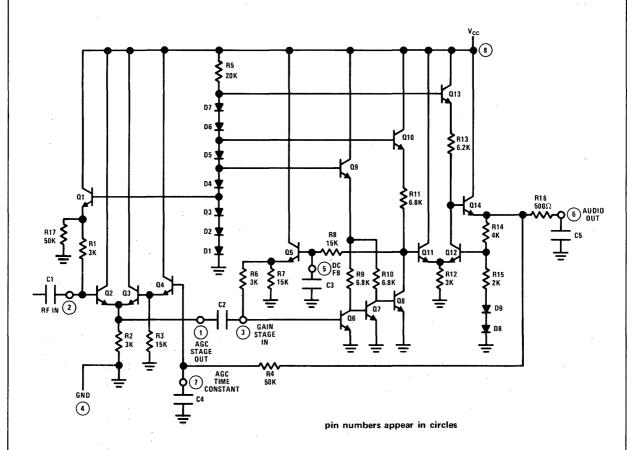

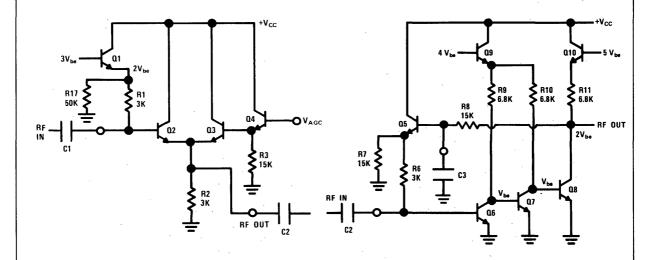

| AN-15          | A Complete Monolithic IF Strip for AM/AGC Applications     | 8/68         |

| AN-20          | An Applications Guide for Op Amps                          | 2/69         |

| AN-21          | Designs for Negative Voltage Regulators                    | 12/68        |

| AN-23          | The LM105 — An Improved Positive Regulator                 | 1/69         |

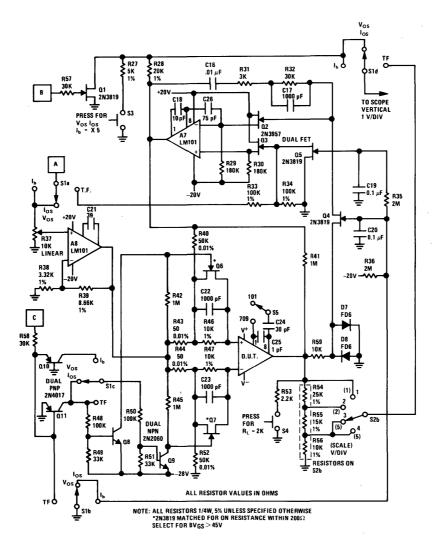

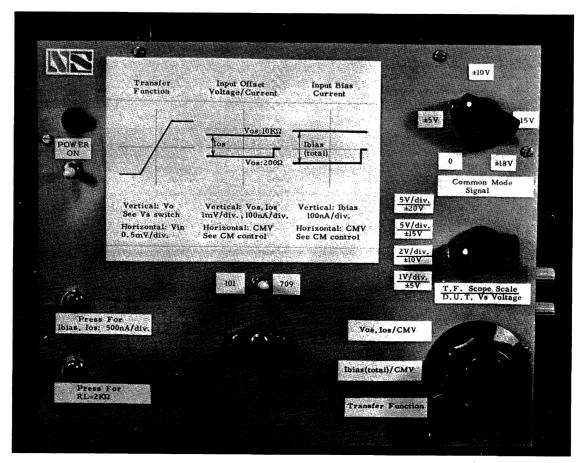

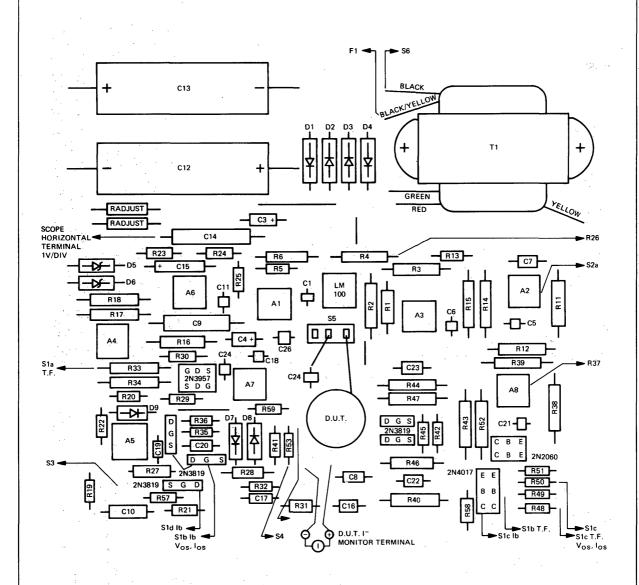

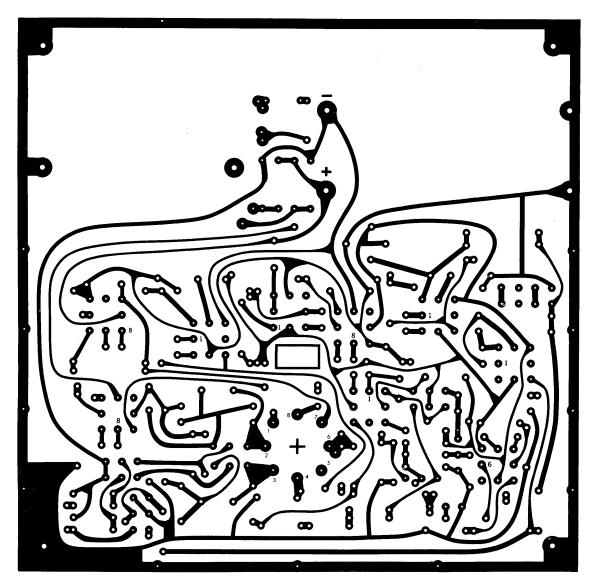

| AN-24          | A Simplified Test Set for Op Amp Characterization          | 6/69         |

| AN-28          |                                                            | 1/70         |

| AN-29          |                                                            | .,           |

| AN-30          |                                                            | 12/69        |

| AN-31          |                                                            | 11/69        |

| AN-32          | Op Amp Circuit Collection                                  | 2/70         |

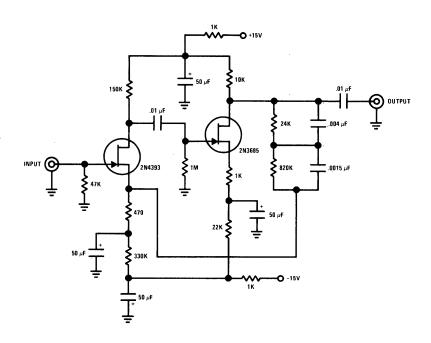

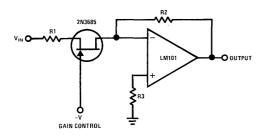

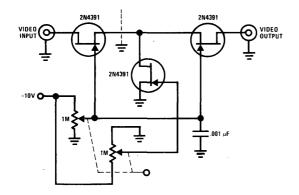

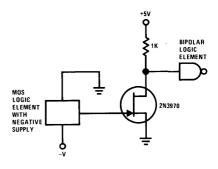

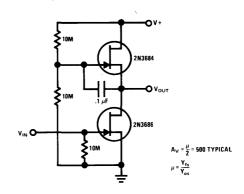

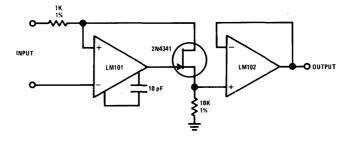

|                | FET Circuit Applications                                   | 2/70         |

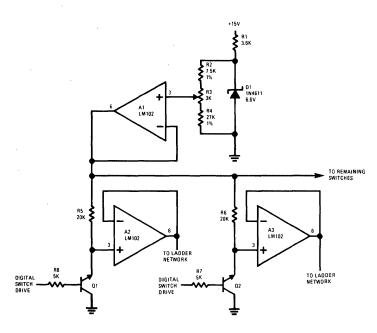

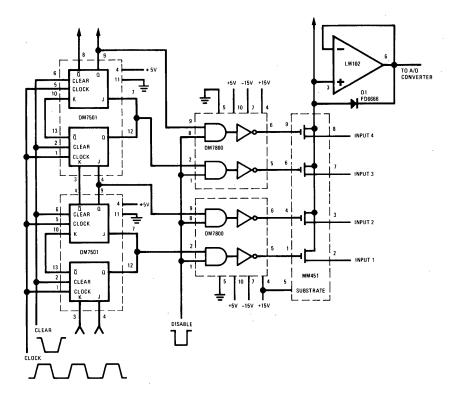

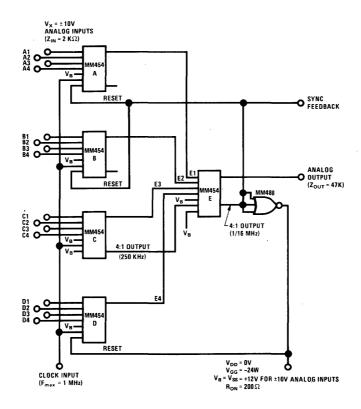

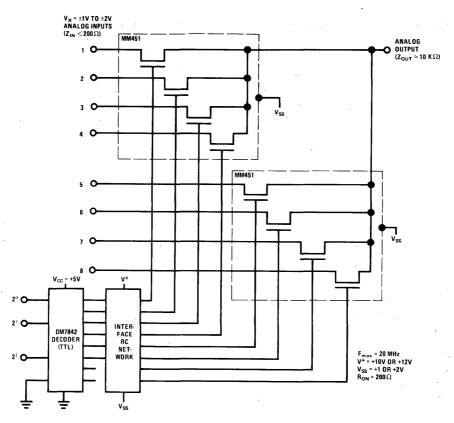

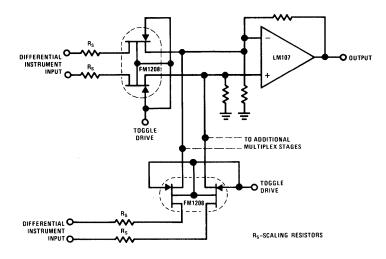

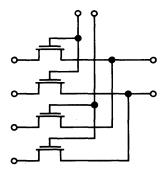

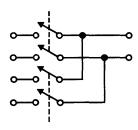

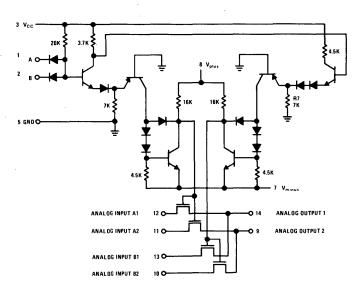

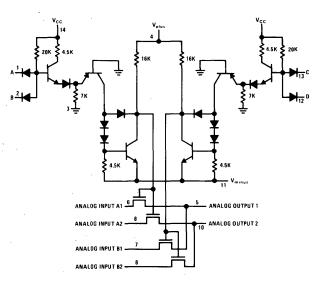

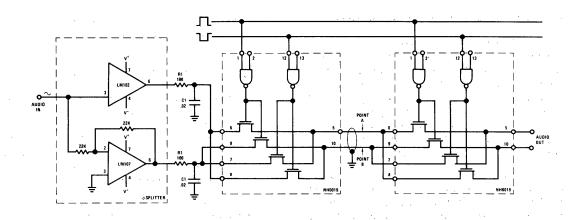

| AN-33          | Analog-Signal Commutation                                  | 2/70         |

| AN-34          | How to Bias the Monolithic JFET Dual                       | 3/70         |

| AN-38          | Applications of MOS Analog Switches                        | 5/70         |

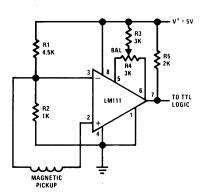

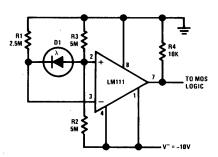

| AN-41          | Precision IC Comparator Runs from +5V Logic Supply         | 10/70        |

| AN-42          | IC Provides On-Card Regulation for Logic Circuits          | 2/71         |

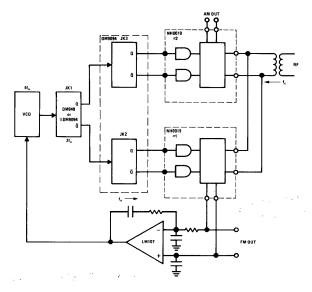

| AN-46          | The Phase Locked Loop IC as a Comm. System Building Block  | 6/71         |

| AN-48          | Applications for a New Ultra-High Speed Buffer             | 8/71         |

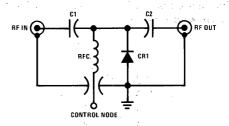

| AN-49          | PIN Diode Drivers                                          | 8/71         |

| AN-51          | A Unique Monolithic AGC/Squelch Amplifier                  | 9/71         |

| AN-53          | High Speed Analog Switches                                 | 9/71         |

| LINEAR BR      | HEFS                                                       |              |

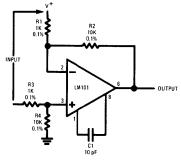

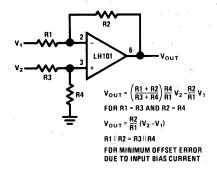

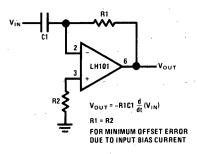

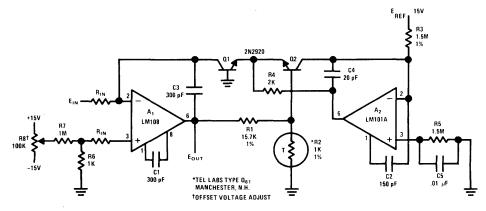

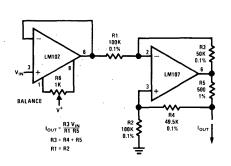

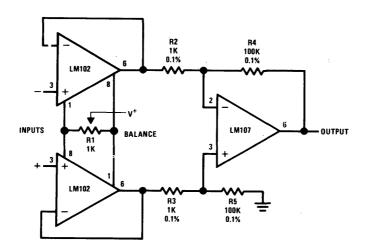

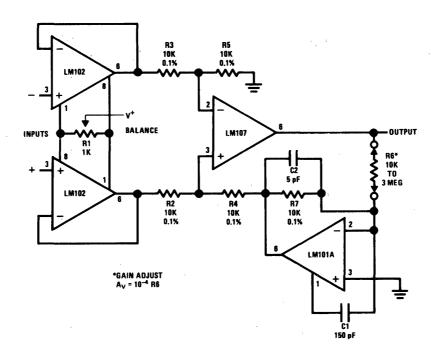

| LB-1           | Instrumentation Amplifier                                  | 3/69         |

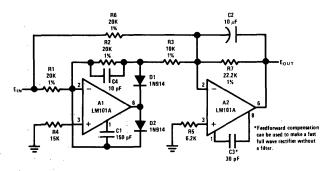

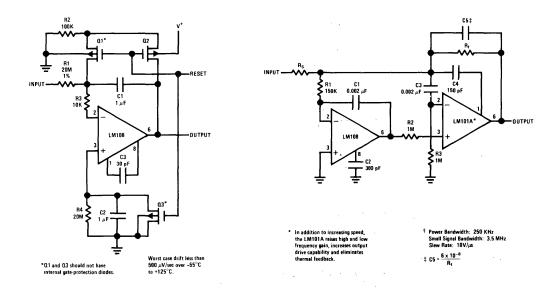

| LB-2           | Feedforward Compensation Speeds Op Amp                     | 3/69         |

| LB-3           | Worst Case Power Dissipation in Linear Regulators          | 4/69         |

| LB-4           | Fast Compensation Extends Power Bandwidth                  | 4/69         |

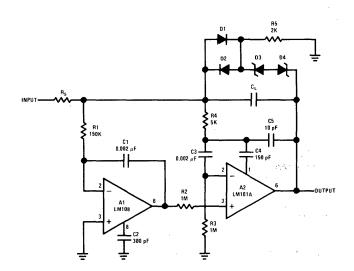

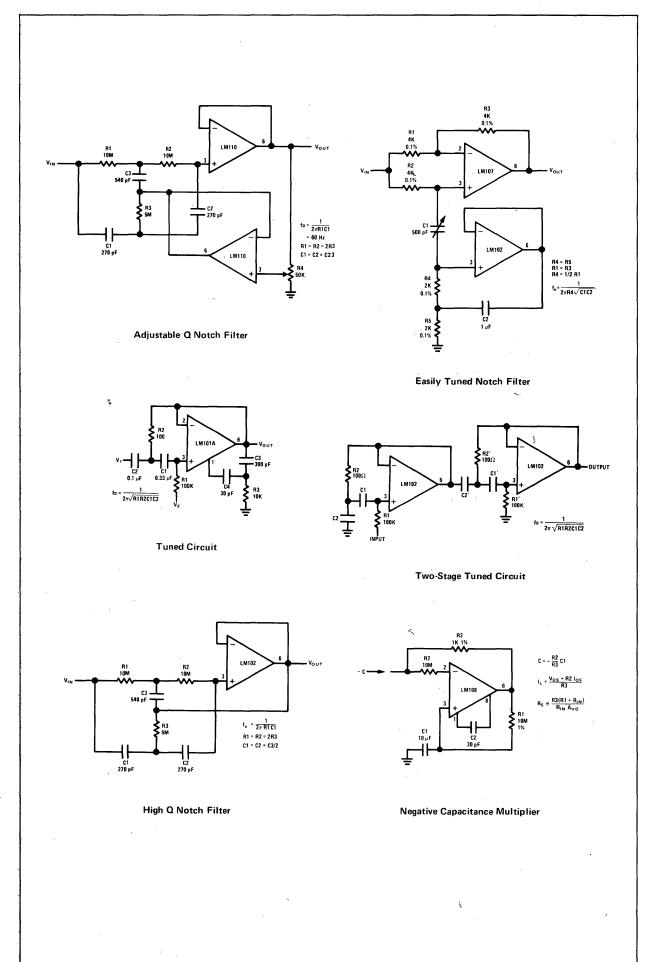

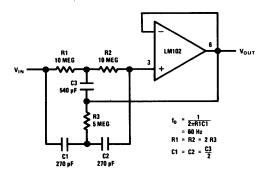

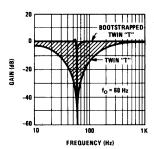

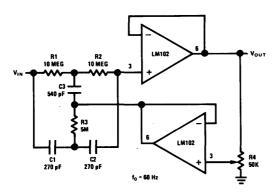

| LB-5           | High Q Notch Filter                                        | 3/69         |

| LB-6           | Fast Voltage Comparators with Low Input Current            | 5/69         |

| LB-7           | Tracking Voltage Regulators                                | 8/69         |

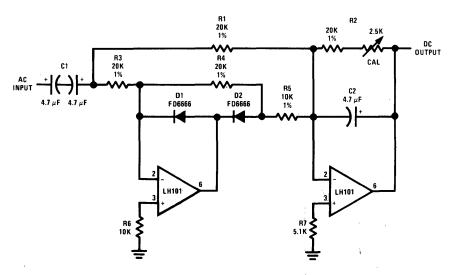

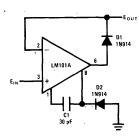

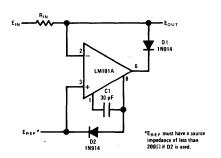

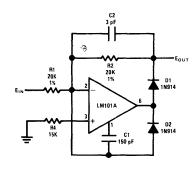

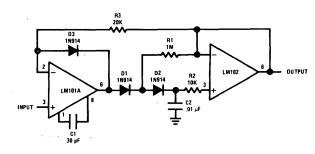

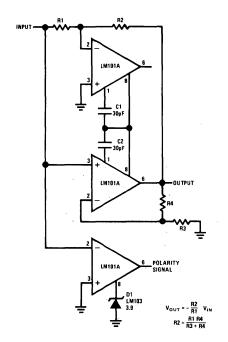

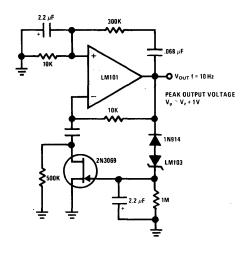

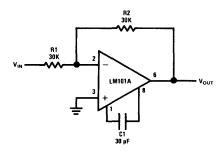

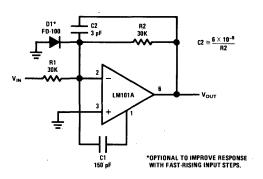

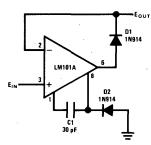

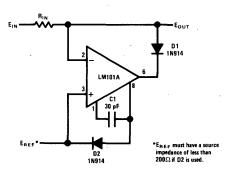

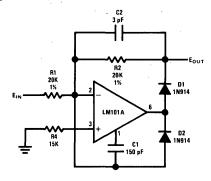

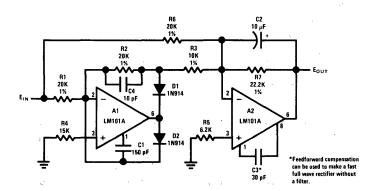

| LB-8           | Precision AC/DC Converters                                 | 8/69         |

| LB-9           | Universal Balancing Techniques                             | 8/69         |

| LB-10          | IC Regulators Simplify Power Supply Design                 | 1/70         |

| LB-11          | The LM110-An Improved IC Voltage Follower                  | 3/70         |

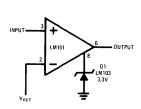

| LB-12          | An IC Voltage Comparator for High Impedance Circuitry      | 3/70<br>1/70 |

| LB-13          | Applications of the LM173/LM273/LM373                      | 11/70        |

| LB-13<br>LB-14 | Speed Up the LM108 Feedforward Compensation                | 11/70        |

| LB-14<br>LB-15 | High Stability Regulators                                  | 1/70         |

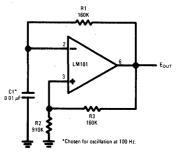

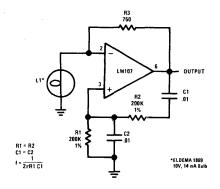

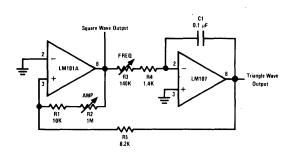

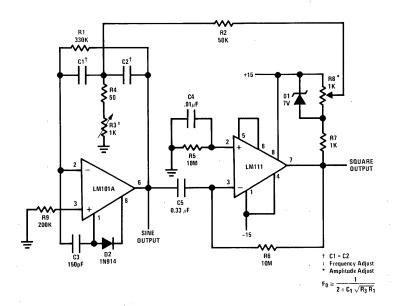

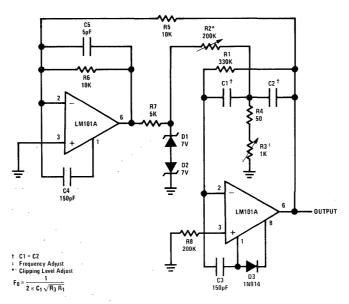

| LB-16          | Easily Tuned Sine Wave Oscillators                         | 3/71         |

| LB-17          |                                                            | -            |

| LU-17          | LM118 Op Amp Slews 70 V/µsec                               | 9/71         |

|                | DEVICE VERGUE ADDITION                                     |              |

|                | DEVICE VERSUS APPLICATION                                  |              |

|                | LITERATURE CROSS-REFERENCE                                 |              |

| DEVICE         | APPLICATION DEVICE APPLIC                                  | ΑΤΙΟΝ        |

| DEVICE              | APPLICATION                | DEVICE | APPLICATION                   |

|---------------------|----------------------------|--------|-------------------------------|

| NUMBER              | LITERATURE                 | NUMBER | LITERATURE                    |

| AM1000              |                            |        | AN-31                         |

| DH0035              |                            |        | 9, AN-30, AN-31, LB-14, LB-15 |

| FETS                | •                          |        | AN-42, LB-15                  |

| LH0001 (NH0001)     | ,                          | LM110  | AN-31, LB-11                  |

| LH0002 (NH0002)     | AN-13                      | LM111  | AN-41, LB-12, LB-16           |

| LH0014 (NH0014)     | AN-38                      | LM118  | LB-17                         |

| LH0019 (NH0019)     | AN-38                      | LM170  | AN-51                         |

| LH0033              | AN-48                      |        | AN-6                          |

| LH101               | AN-20                      | LM172  | AN-15                         |

| LM100               | . AN-1, AN-2, AN-8, LB-3   | LM173  | LB-13                         |

| LM101               | AN-3, AN-4, AN-20, AN-24   | LM565  | AN-46                         |

| LM101A AN-30, AN-31 | , LB-2, LB-4, LB-8, LB-16  | LM703  | AN-6                          |

| LM102 AN-           | 5, AN-31, LB-1, LB-5, LB-6 | LM709  | AN-24                         |

| LM104               | AN-21, LB-3, LB-7, LB-10   | MM450  | AN-33                         |

| LM105 <del></del>   | AN-23, LB-7, LB-10         | MM451  | AN-33                         |

| LM106               | LB-6                       | MM454  | AN-28, AN-33                  |

#### SUBJECT INDEX

Converter: LB6-1 Ladder Driver: AN5-7

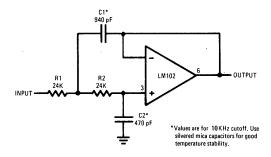

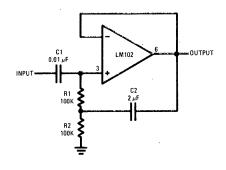

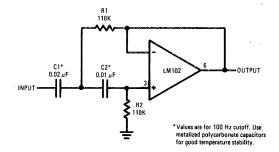

ABSOLUTE VALUE AMPLIFIER: AN31-12 AC AMPLIFIERS: AN5-9, AN31-1, AN31-18, AN48-4 AC TO DC CONVERTER: AN31-12, LB-8 **ACTIVE FILTERS (see Filter, Active)** AGC

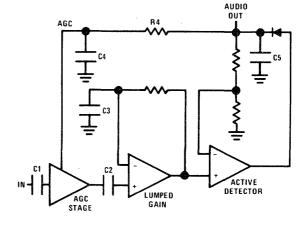

AGC/Squelch amplifier: AN51

AM/IF AGC: AN15

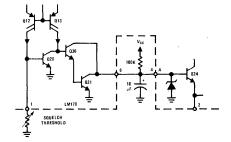

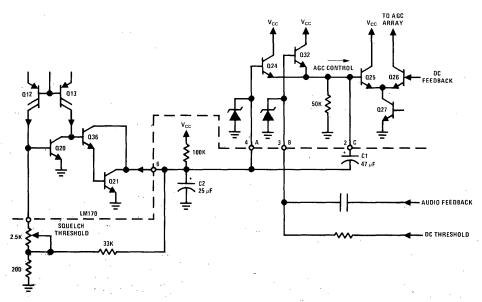

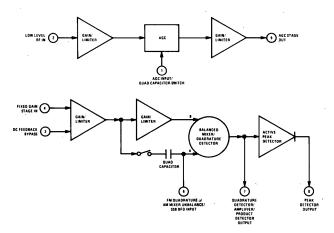

Circuit description, LM170/LM270/LM370: AN51-3

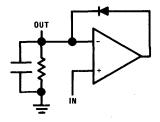

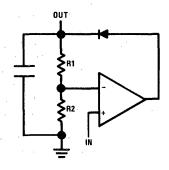

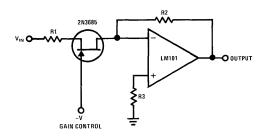

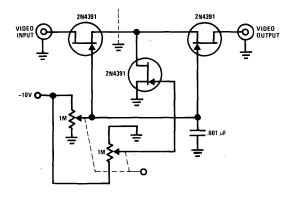

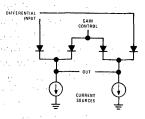

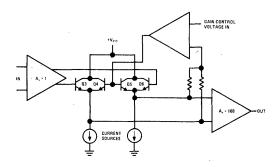

Element comparison: AN51-1 FET amplifier: AN34-2 Hints: AN51-4 Methods: AN51-1

RF Cascode amplifier: AN6-3 Temperature compensation: AN51-11

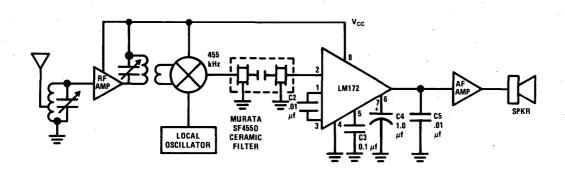

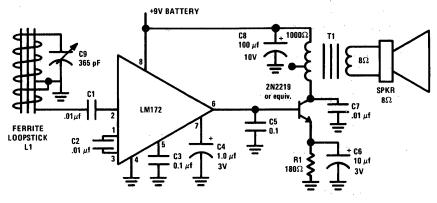

AM/FM DEMODULATOR: AN38-7, AN46-11, LB-13 AM/IF STRIP: AN15

**AMPLIFIER**

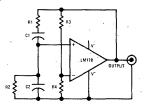

AC: AN5-9, AN31-1, AN31-18, AN48-4

Absolute Value: AN31-12

Anti-Log Generator: AN30-3, AN31-20

Audio, J-FET: AN32-5 Bridge: AN29-12, AN31-11

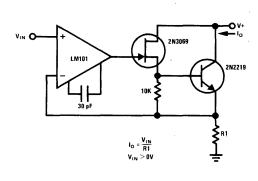

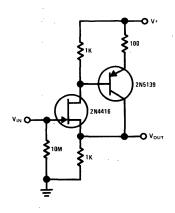

Buffered High Current Output: AN4-3, AN13-3, AN29-15,

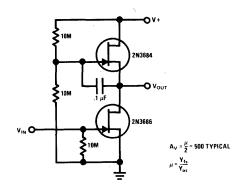

AN31-16, AN48-1, AN48-4 Cascode, FET: AN32-2, AN32-6

Cascode, RF: AN6-1, AN6-3, AN6-4, AN32-9

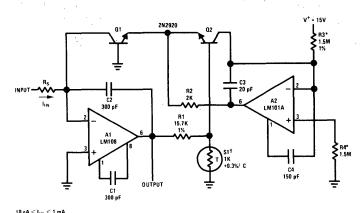

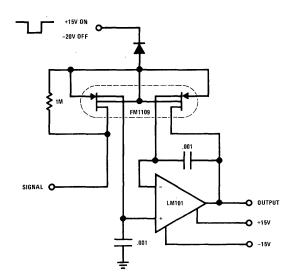

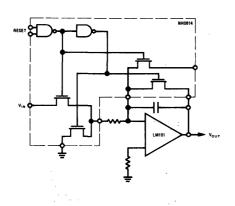

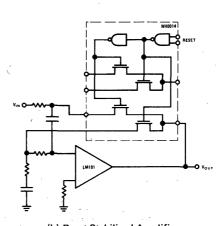

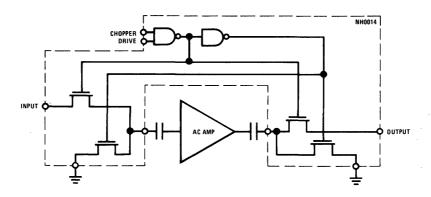

Chopper stabilized: AN38-4

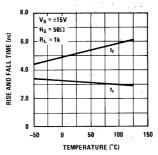

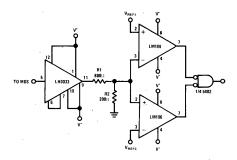

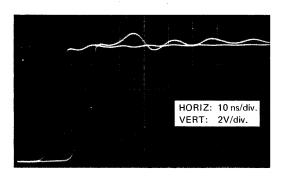

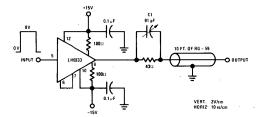

Circuit description: LH00033: AN48-1

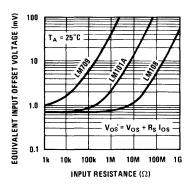

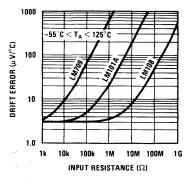

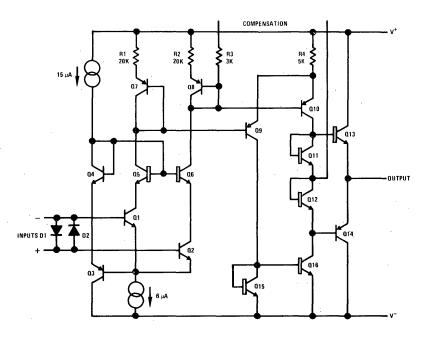

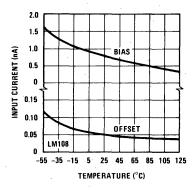

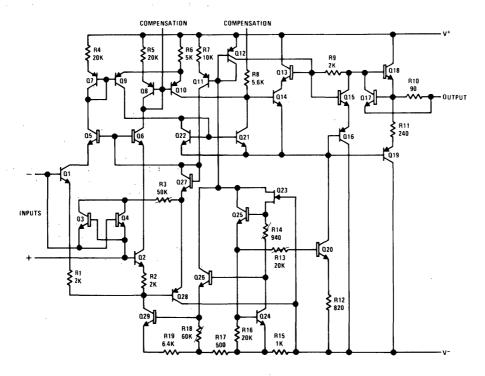

Circuit description: LM108/LM208/LM308: AN29-2,

AN29-18

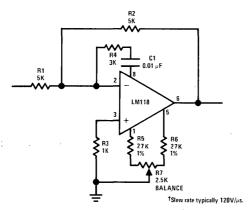

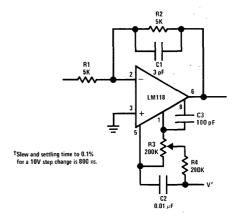

Circuit description: LM118/LM218/LM318: LB-17

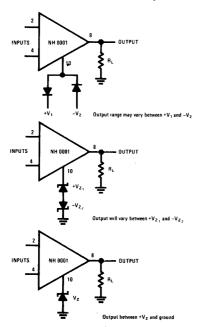

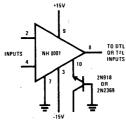

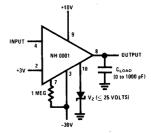

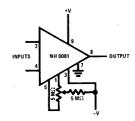

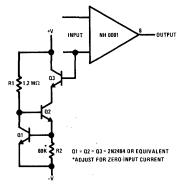

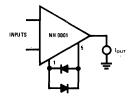

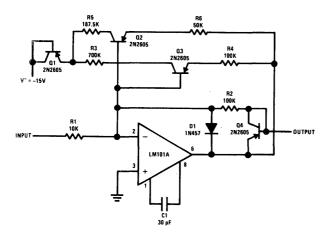

Circuit description: NH0001: AN10-1 Circuit description: NH0002: AN13-2 Clamping: AN10-2, AN31-11, LB8-1

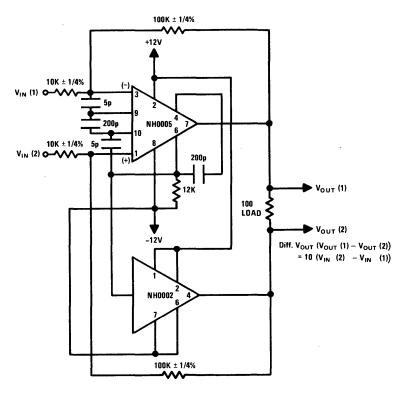

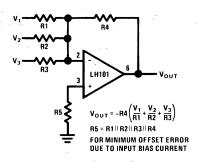

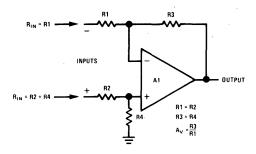

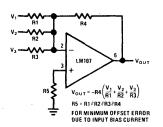

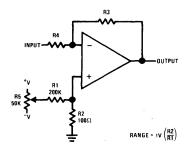

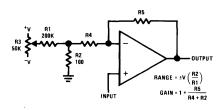

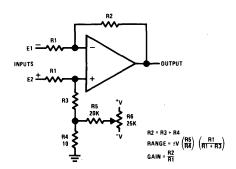

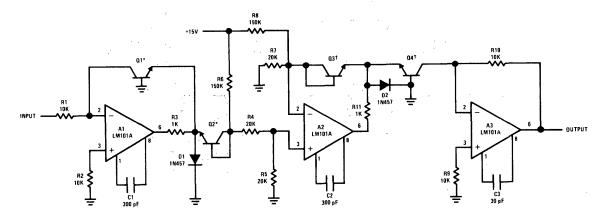

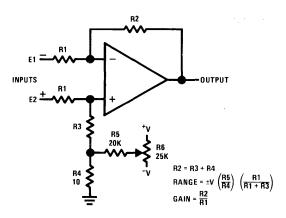

Difference: AN20-3, AN29-12, AN31-1, AN31-9, AN31-10

Differentiator: AN20-3, AN31-2

FFT: AN34

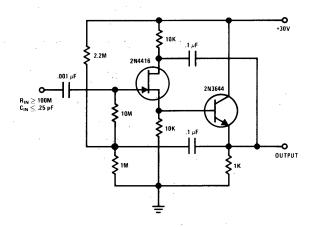

FET input: AN4-3, AN29-1, AN32-9, AN34-3

Follower (see Voltage Follower)

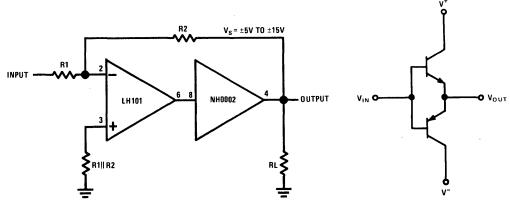

High current buffer: AN4-3, AN13, AN29-15, AN31-16,

AN48-1, AN48-4

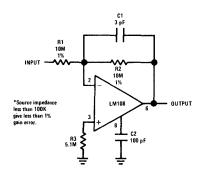

High input impedance: AN29-14, AN31-1, AN31-11, AN31-18

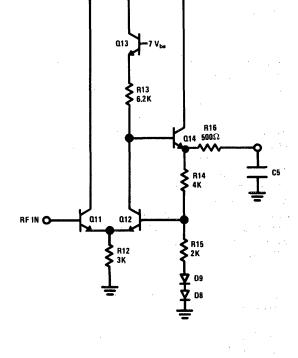

AN32-1, AN32-7, AN48-4, LB1-2 IF: AN6-5, AN15-2, AN15-5, LB13

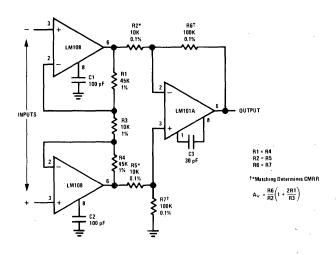

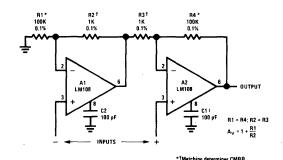

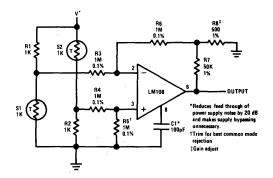

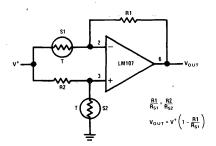

Input guarding: AN29-16 Instrumentation: AN29-11, AN31-9, AN31-10, AN31-11, LB1

Instrumentation shield/line driver: AN48-3

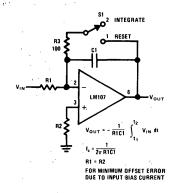

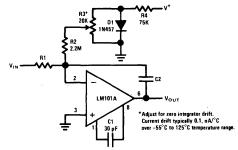

Integrator: AN20-4, AN29-7, AN31-2, AN31-3, AN31-13, AN38-4

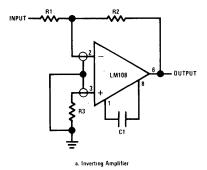

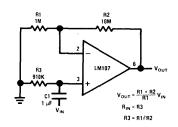

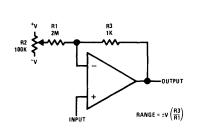

Integrator, J-FET AC coupled: AN32-1 Inverting: AN20-1, AN31-1, AN31-4, LB17-2

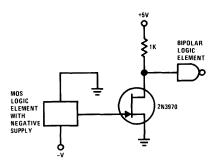

Level shifting: AN4-2, AN13-4, AN32-5, AN41-3, AN48-3

Line driver: AN13-4

Logarithmic converter: AN29-12, AN30, AN31-18, AN31-20 Low power: AN10

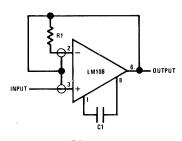

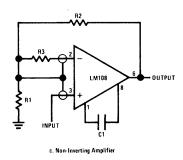

Non-inverting amplifier: AN20-2, AN31-1, AN31-4

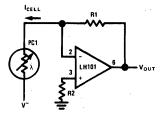

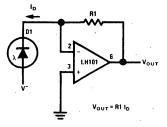

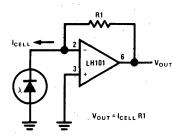

Non-linear: AN4-4, AN31-16 Output resistance: AN29-5 Photocell: AN20-5, AN20-8

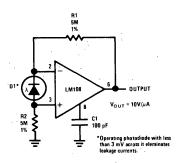

Photodiode: AN20-5, AN29-13, AN31-3, AN31-18, LB12-2 Photoresistor bridge: AN29-12

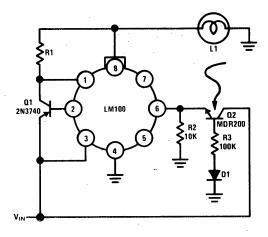

Phototransistor: AN8-8

Piezoelectric transducer: AN29-13, AN31-17 Power: AN8-6 (see also Buffer, High Current)

Pulse: AN8-11, AN13-4

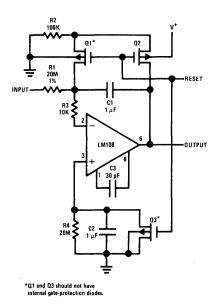

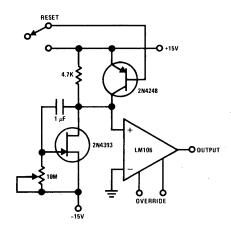

Rejection, power supply: AN29-6 Reset stabilized: AN20-7, AN38-4

RF (see RF Amplifier)

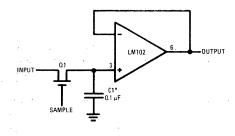

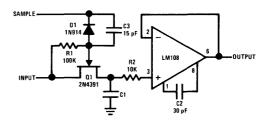

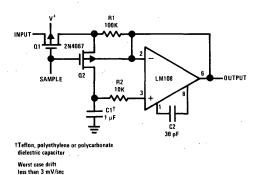

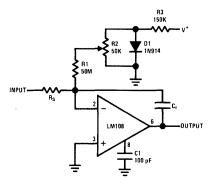

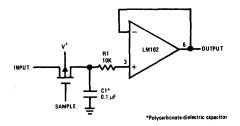

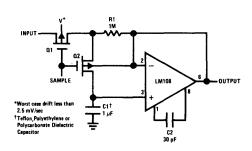

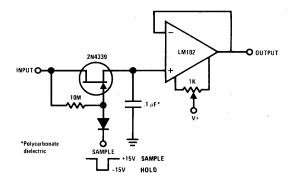

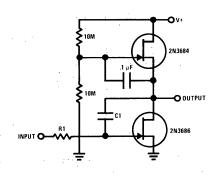

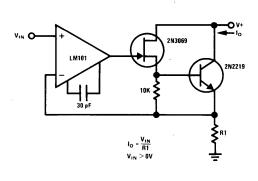

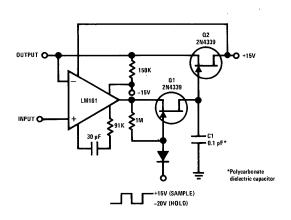

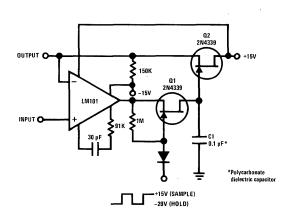

Sample and hold: AN4-3, AN5-8, AN29-6, AN31-12, AN32-1

AN32-6, AN32-7, AN48-3, LB11-2 Servo preamplifier: AN4-4, AN31-16

Squelch, AGC: AN51

Solar cell: AN4-5

Summing: AN20-3, AN31-1, AN31-13

Temperature probe: AN31-17

Variable gain: AN31-9, AN31-15, AN32-5, LB1-2 (see also AGC)

ANALOG COMMUTATOR (see Analog Switch) ANALOG DIVIDER: AN4-5, AN30-4, AN31-19

ANALOG MULTIPLIER: AN4-5, AN20-8, AN30-4, AN31-15,

AN31-17, AN31-19

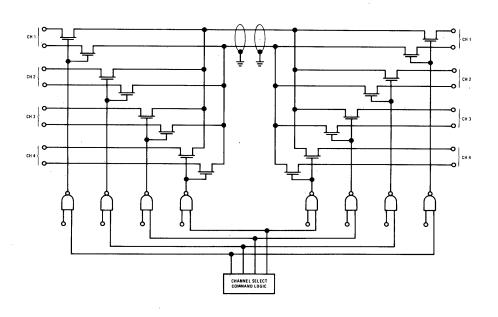

ANALOG SIGNAL, DEFINITION: AN53-1

ANALOG SWITCH: AN5-8, AN28, AN32-4, AN32-8, AN32-9

AN32-10, AN32-12, AN33, AN38, AN53

ANALOG TO DIGITAL

Converter: LB6-1 Ladder driver: AN5-7

ANTI-LOG GENERATOR: AN30-3, AN31-20 AUDIO J-FET AMPLIFIER: AN32-5 AUTOMATIC GAIN CONTROL (see AGC)

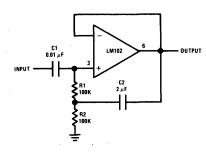

BANDPASS FILTER: LB11-2 (see also Notch Filter) BANDWIDTH, EXTENDED: AN29-5, LB2, LB4, LB14 BIAS CURRENT COMPENSATION (see Drift Compensation)

**BIAS CURRENT TEST SET: AN24-2**

BIASING, FET: AN34

**BOARD LAYOUT: AN29-16**

BOOTSTRAPPED SHUNT FREQUENCY COMPENSATION:

BRIDGE AMPLIFIER: AN29-12, AN31-11

BUFFER, HIGH CURRENT: AN4-3, AN13-3, AN29-15, AN31-16,

AN48-1, AN48-4

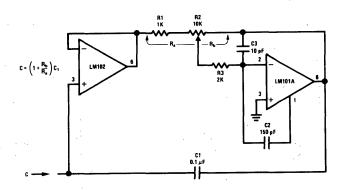

BYPASSING, SUPPLY TERMINAL: AN4-8, LB2-2, LB15-1 CAPACITANCE MULTIPLIER: AN29-10, AN31-14, AN31-15

CAPACITOR

Bypass: AN4-8, LB2-2, LB15-1

Compensation: AN29-4 (see also Frequency Compensation)

Dielectric polarization: AN29-7 Filter, power supply: AN23-7, LB10-2

Multiplier, capacitance: AN29-10, AN31-14, AN31-15

Switching regulator filter: AN21-11

Tantalum bypass: LB15-1

CASCODE AMPLIFIER: AN6-1, AN6-3, AN6-4, AN32-2, AN32-6,

AN32-9

CHOPPER STABILIZED AMPLIFIER: AN38-4

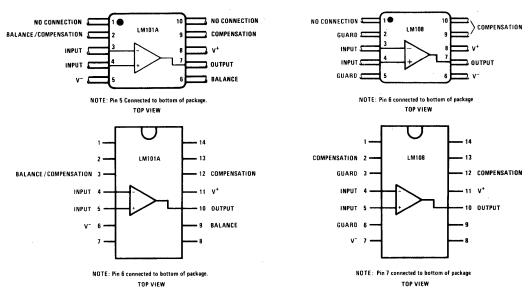

CIRCUIT DESCRIPTIONS

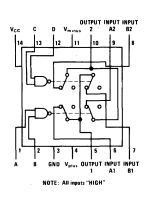

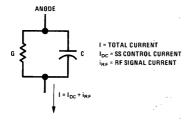

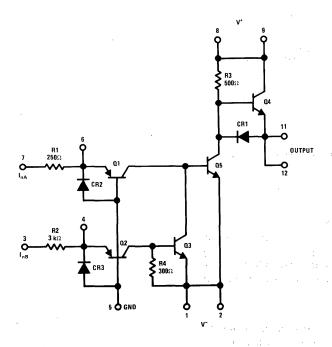

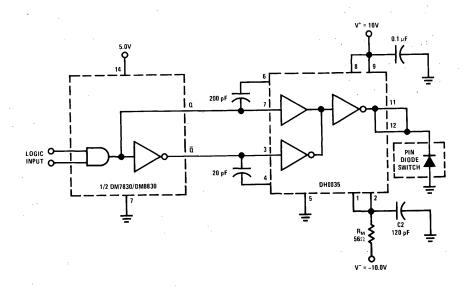

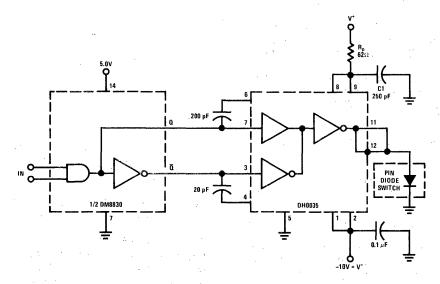

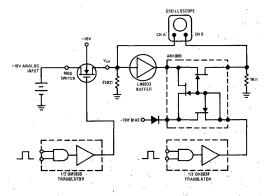

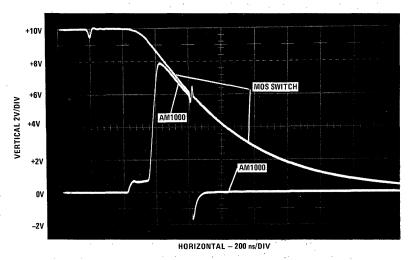

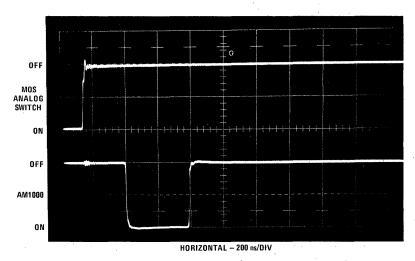

AM1000 Analog switch series: AN53-2 DH0035, PIN diode driver: AN49-2 LH00033 Buffer amplifier: AN48-1

LM100/LM200/LM300 Positive voltage regulator: AN1-2,

AN8-1

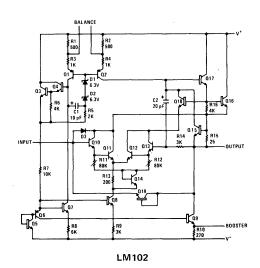

LM102/LM202/LM302 Voltage follower: AN5-1

LM104/LM204/LM304 Negative voltage regulator: AN21-1

AN21-15

LM105/LM205/LM305 Positive voltage regulator: AN23-1, AN23-2

LM108/LM208/LM308 Operational amplifier: AN29-2, AN29-18

LM109/LM209/LM309 Three terminal regulator: AN42-1

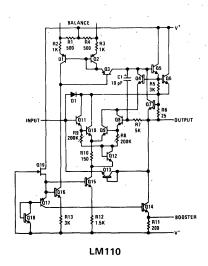

LM110/LM210/LM310 Voltage follower: LB11

LM111/LM211/LM311 Voltage comparator: AN41-1, LB12 LM118/LM218/LM318 High slew rate op. amp.: LB17 LM170/LM270/LM370 AGC squelch amplifier: AN51-3

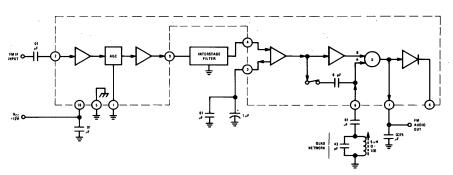

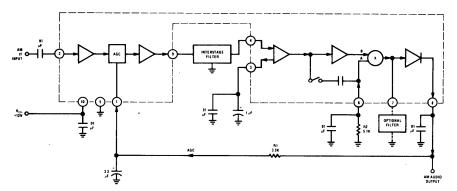

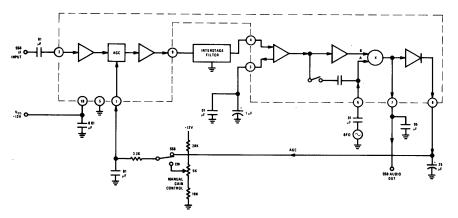

LM172 AM/IF strip: AN15-1, AN15-4

LM173/LM273/LM373, IF amplifier/detector: LB13

LM565 Phase locked loop: AN46-5 NH0001 low power op. amp.: AN10-1 NH0002 Current amplifier: AN13-2

CLAMP

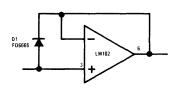

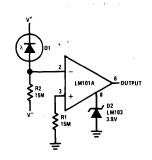

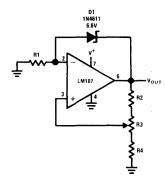

Operational amplifier: AN10-2 Precision: AN31-11, LB8-1 Voltage follower input: AN5-5

COMPARATOR (see Voltage Comparator)

COMPENSATION, DRIFT (see Drift Compensation)

COMPENSATION, FREQUENCY (see Frequency Compensation) COMPENSATION, TEMPERATURE (see Drift Compensation)

CONVERTER

100 MHz: AN32-3 AC to DC: AN31-12, LB8

Analog to digital: LB6-1 Current to voltage: AN20-5, AN31-2, AN31-16

Digital to analog: AN48-3

Logarithmic: AN29-12, AN30, AN31-18, AN31-20

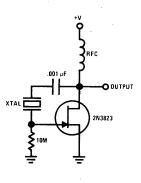

CRYSTAL OSCILLATOR: AN32-2, AN32-8, AN41-4 CUBE GENERATOR: AN30-3, AN31-19

**CURRENT LIMITING**

Adjustable: AN21-7 External: AN21-9, AN29-16

Foldback (see Foldback Current Limiting)

Output short circuit: AN10-3

Sense voltage reduction: AN21-4, AN21-7, AN31-16, AN32-11

#### SUBJECT INDEX (cont'd)

Switchback (see Foldback Current Limiting) Switching regulator: AN2-8, AN8-4, AN21-12 Voltage regulator, positive: AN1-5

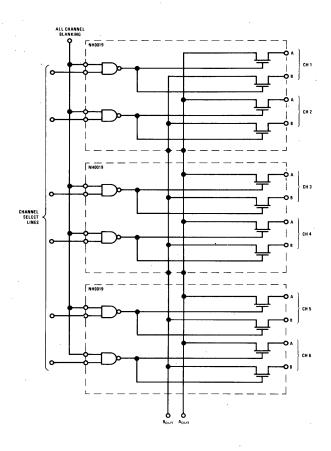

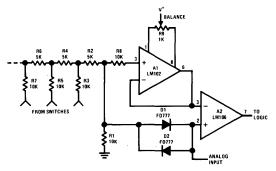

**CURRENT MODE MULTIPLEXING: AN53-5**

CURRENT MONITOR: AN31-16, AN32-11 (see also Current to

Voltage Converter) CURRENT SINK, PRECISION: AN20-6, AN31-8, AN32-6

**CURRENT SOURCE**

Bilateral: AN29-14, AN31-6

Floating: AN8-4

Focus control current source: AN8-3 High current: AN8-4, AN42-6 Precision: AN20-6, AN31-8, AN32-12 Switching current regulator: AN8-4

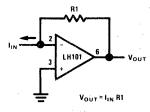

CURRENT-TO-VOLTAGE CONVERTER: AN20-5, AN31-2

AN31-16

D TO A CONVERTER: AN48-3

**DEMODULATOR**

AM-FM: AN38-7, AN46-11, LB13 DSB: AN38-5, AN38-6

Frequency shift keying: AN46-9 IRIG Channel: AN46-8

SSB: LB13-2

Weather satellite picture: AN46-11

**DIELECTRIC POLARIZATION, CAPACITOR: AN29-7**

DIFFERENCE AMPLIFIER: AN20-3, AN29-12, AN31-1,

AN31-9, AN31-10

DIFFERENTIATOR: AN20-3, AN31-2

**DIGITAL TO ANALOG CONVERTER: AN48-3**

DIODE

Catch: AN21-11 PIN driver: AN49 Precision: AN31-11, LB8-1 Protective: AN21-8

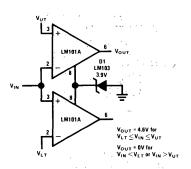

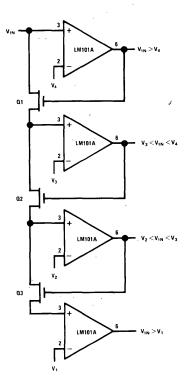

DISCRIMINATOR, MULTIPLE APERTURE WINDOW: AN31-3

DIVIDER, ANALOG: AN4-5, AN30-4, AN31-19 **DOUBLE ENDED LIMIT DETECTOR: AN31-3** DOUBLER, FREQUENCY: AN41-4

**DRIFT COMPENSATION**

AGC Gain: AN51-11

Bias current: AN3-1, AN10-3, AN20-1, AN29-8, AN31-3

Board layout: AN29-16

Chopper stabilized amplifier: AN38-4

Gain, AGC: AN51-11

Integrator, low drift: AN31-13 Non-linear amplifiers: AN4-4, AN31-16 Offset voltage: AN3-3, AN20-1, AN31-4 Reset stabilized amplifier: AN20-7 Sample and hold: AN4-4, AN29-7

Voltage regulator: AN1-10, AN8-11, AN21-4, AN23-4

AN42-6, LB15

DRIFT, VOLTAGE AND CURRENT: AN29-1 (see also Drift

Compensation)

DRIVER (see Amplifier, High Current Buffer) DSB MODULATION-DEMODULATION: AN38-5, AN38-6 EMITTER COUPLED RF AMPLIFIER: AN6-1, AN6-2

Amplifier: AN32, AN34

Biasing: AN34

Operational amplifier input: AN4-3, AN29-1, AN32-9, AN34-3 Switches: AN5-8, AN28, AN32-4, AN32-8, AN32-9, AN32-10

AN32-12, AN33, AN38, AN53 Voltage comparator: AN34-2 Voltmeter, FETVM: AN32-2

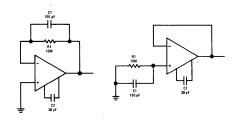

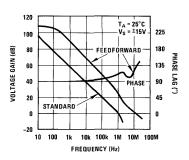

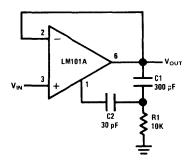

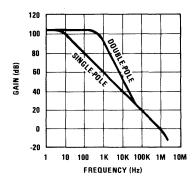

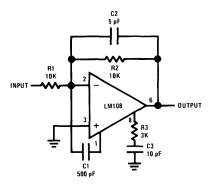

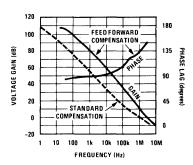

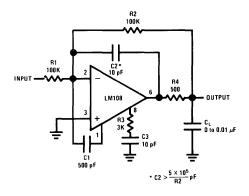

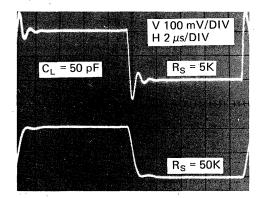

FEEDFORWARD COMPENSATION: LB2, LB14, LB17-2

FERRITE BEAD: AN23-6

Adjustable Q: AN31-14, LB5-2

Bandpass: LB11-2 (see also Filter, Notch)

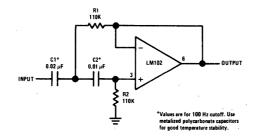

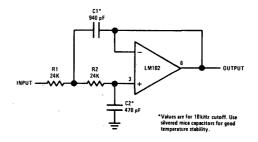

Full wave rectifying and averaging: AN20-8, AN31-12 High pass active filter: AN5-10, AN31-16, LB11-2 Low pass active filter: AN5-9, AN20-4, AN31-16 Notch: AN31-14, AN48-4, LB5, LB11-2

Notch, adjustable Q: AN31-14, LB5-2 Power supply: -AN23-7, LB10-2 Tone Control: AN32-3, AN32-11

FOLDBACK CURRENT LIMITING

Negative voltage regulator: AN21-5, LB3-2 Positive voltage regulator: AN1-8, AN23-5,

Power dissipation curve: AN23-6 Temperature sensitivity: AN23-6

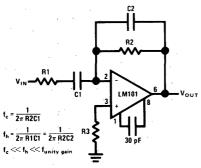

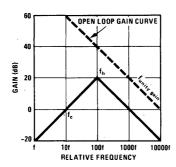

FREQUENCY COMPENSATION

Bandwidth, extended: AN29-5, LB2, LB4, LB14

Bootstrapped shunt: AN29-16 Capacitance, stray: AN4-8, AN31-3 Capacitive loads: AN4-8, LB14-1

Differentiator: AN20-4

Feedforward: LB2, LB14, LB17-2

Ferrite bead: AN23-6

Hints: AN4-7, AN20-2, AN23-6, AN41-5, LB2, LB4

Multivibrator: AN4-1

Oscillation, involuntary: AN4-8, AN20-2, AN29-5

FREQUENCY DOUBLER: AN41-4

FREQUENCY RESPONSE (see Frequency Compensation)

FREQUENCY SHIFT KEYING DEMODULATOR: AN46-9

GAIN TEST SET: AN24-4 **GENERATOR** (see Oscillator) **GUARD DRIVER: AN48-3**

**GUARDING AMPLIFIER INPUTS: AN29-16**

HIGH PASS ACTIVE FILTER: AN5-10, AN31-16, LB11-2

IF AMPLIFIER: AN6-5, AN15-2, AN15-5, LB13

INDUCTOR

Core, switching regulator: AN21-11

Ferrite bead: AN23-6 Simulated: AN31-15

INSTRUMENTATION AMPLIFIER: AN29-11, AN31-9, AN31-10

INTEGRATOR: AN20-4, AN29-7, AN31-2, AN31-3, AN31-13

AN32-1, AN38-4

INTERNAL TIMER: AN31-17

INVERTING AMPLIFIER: AN20-1, AN31-1, AN31-4, LB17-2

ISOLATION, DIGITAL: AN41-3

LAMP DRIVER, VOLTAGE COMPARATOR: AN4-2, LB12-2 LEVEL SHIFTING AMPLIFIER: AN4-2, AN13-4, AN32-5,

AN41-3, AN48-3

LIGHT-INTENSITY REGULATOR: AN8-8

**LIMIT DETECTOR: AN31-3**

LIMITER, (see Clamp) LINE DRIVER: AN13-4, AN48-3

LOGARITHMIC AMPLIFIER: AN29-12, AN30, AN31-18,

LOW PASS ACTIVE FILTER: AN5-9, AN20-4, AN31-16

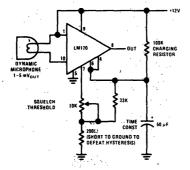

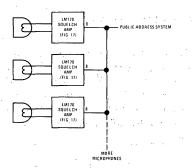

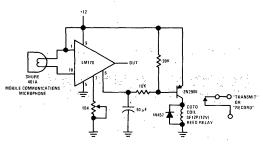

MICROPHONE PREAMPLIFIER: AN51-7

MODULATION

Voltage regulator, switching: AN8-6

MODULATOR

AM/IF: AN51-9 DSB: AN38-5 Pulse width: AN31-5 SSB, high efficiency: AN8-6

MULTIPLEXER (see Analog Switch) MULTIPLEXING, DEFINITION: AN53-1

MULTIPLIER

Analog: AN4-5, AN20-8, AN30-4, AN31-15, AN31-17, AN31-19

Capacitance: AN29-10, AN31-14, AN31-15

Cube generator: AN30-3, AN31-19

Resistance: AN29-14

MULTIVIBRATOR: AN4-1, AN24-6, AN31-6, AN41-4 NEGATIVE AND POSITIVE VOLTAGE REGULATORS (see

Symmetrical Voltage Regulators)

NEGATIVE SWITCHING VOLTAGE REGULATOR: AN2-10,

AN21-10, AN21-11, AN21-12, AN21-13

NEGATIVE VOLTAGE REFERENCE: AN20-6, AN31-8

NEGATIVE VOLTAGE REGULATOR

Circuit description LM104/LM204/LM304: AN21-1, AN21-15 Drift compensation (see Drift Compensation, Voltage Regulator)

Foldback current limiting: AN21-5, LB3-2 High current: AN21-3, AN21-4, AN21-5, LB10

High voltage: AN21-9 Hints: LB10-2, LB15

LM100 as a negative regulator: AN1-9 Line regulation improvement: AN21-7 Overvoltage protection: AN21-8 Power dissipation: AN21-3, AN21-5

#### SUBJECT INDEX (cont'd)

Precision stable: LB15-2

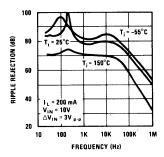

Programmable: AN20-11, AN31-7 Protective diodes: AN21-8 Remote sensing: AN21-4, AN21-9 Ripple: AN21-2, AN21-6

Shunt regulator: AN8-1 Transient response: AN21-2

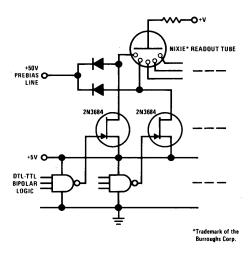

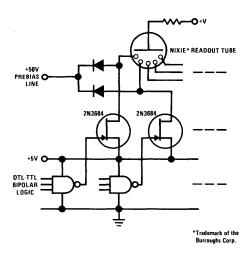

**NIXIE DRIVER: AN32-6**

NON-INVERTING AMPLIFIER: AN20-2, AN31-1, AN31-4

NON-LINEAR AMPLIFIER: AN4-4, AN31-16 NOTCH FILTER: AN31-14, AN48-4, LB5, LB11-2 OFFSET CURRENT TEST SET: AN24-3

OFFSET VOLTAGE ADJUSTMENT: LB9 OFFSET VOLTAGE COMPENSATION (see Drift Compensation)

OFFSET VOLTAGE TEST SET: AN24-3

OPERATIONAL AMPLIFIERS: AN4, AN20, AN29, AN31 (also

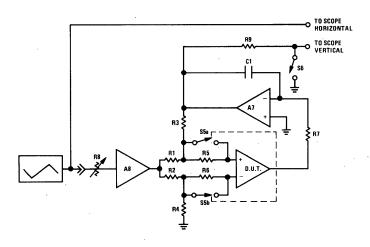

OPERATIONAL AMPLIFIER TEST SET: AN24

OSCILLATION, INVOLUNTARY (see Frequency Compensation)

OSCILLATOR

Crystal: AN41-4

Crystal J-FET: AN32-2, AN32-8

Modulated RF: AN51-9

Multivibrator: AN4-1, AN24-6, AN31-6, AN41-4

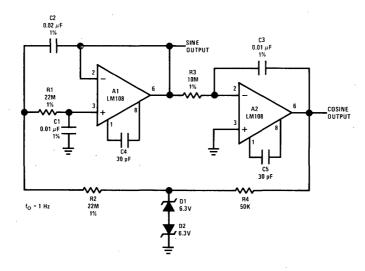

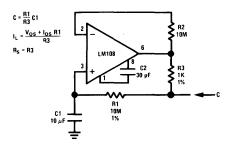

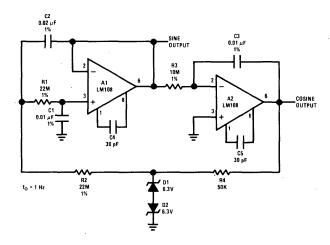

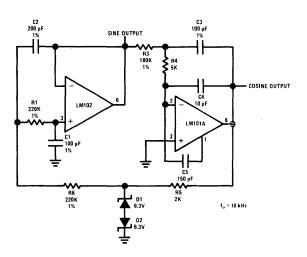

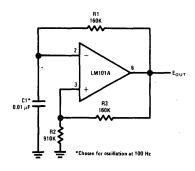

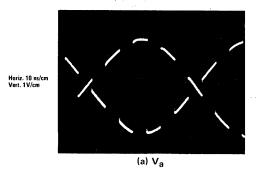

Quadrature output: AN31-5, LB16

RF J-FET: AN32-2, AN32-8

Sine Wave: AN20-9, AN29-9, AN31-5, AN31-6, AN31-7,

AN32-7, AN32-8, AN51-8, LB16 Triangle wave: AN20-10, AN24-6, AN31-6 Tunable frequency: AN51-9, LB16

Wein Bridge: AN20-9, AN31-6, AN31-7, AN32-7, AN51-8

PEAK DETECTOR: AN4-4, AN31-12, AN51-5, AN51-6

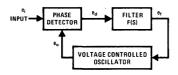

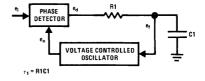

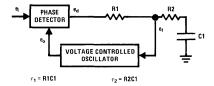

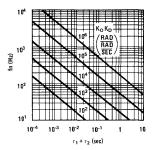

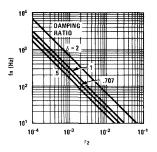

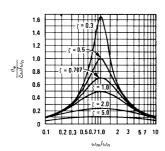

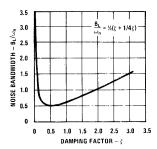

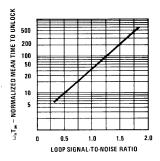

PHASE LOCKED LOOP: AN46

Circuit description, LM565: AN46-5

Damping: AN46-3 Locking: AN46-5 Loop filter: AN46-2 Noise performance: AN46-5 Theory: AN46-1

PHASE SHIFTER: AN32-8

PHONO PREAMPLIFIER: AN32-4, AN32-11 PHOTOCELL AMPLIFIER: AN20-5, AN20-8

PHOTODIODE

Amplifier: AN20-5, AN29-13, AN31-3, AN31-18, LB12-2

Level detector: AN41-2

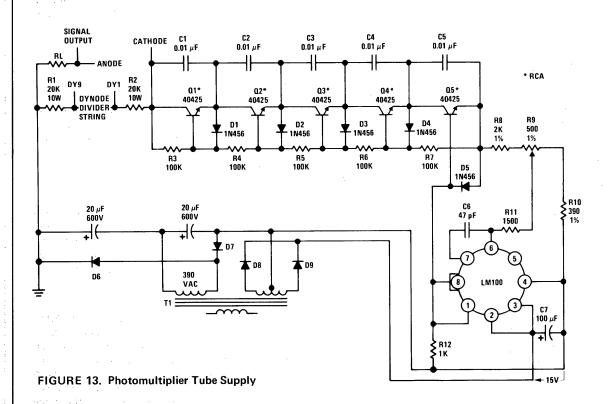

PHOTOMULTIPLIER TUBE SUPPLY: AN8-9 PHOTORESISTOR BRIDGE AMPLIFIER: AN29-12 PHOTOTRANSISTOR AMPLIFIER: AN8-8

PIN DIODE DRIVER: AN49 POLARIZATION, DIELECTRIC: AN29-7

POSITIVE AND NEGATIVE VOLTAGE REGULATORS (see

Symmetrical Voltage Regulators)

POSITIVE VOLTAGE REFERENCE: AN20-6, AN31-2, AN31-8

POSITIVE VOLTAGE REGULATOR

Adjustable output, LM109: AN42-5

Circuit description, LM100/LM200/LM300: AN1-2, AN8-1 Circuit description, LM105/LM205/LM305: AN23-1, AN23-2 Circuit description, LM109/LM209/LM309: AN42-1 Current limit: AN1-5

Drift compensation (see Drift Compensation, Voltage Regulator)

Efficiency: AN1-8

Failure mechanisms: AN23-7, LB3 Filtering, power supply: AN23-7, LB10-2

Fixed output: AN42-5

Foldback current limiting: AN1-8, AN23-5, LB3-2 Heat dissipation: AN1-8, AN23-3, AN23-6, AN23-7, LB3 High current: AN1-7, AN23-4, AN23-5, AN23-6, LB3, LB10-1

High voltage: AN8-8, AN8-9 Hints: AN23-7, LB3, LB10-2, LB15 Impedance, output: AN1-6 Noise reduction: AN1-6

NPN pass transistors: AN8-10, LB10-1 Power limitations: AN23-3, LB3

Precision: AN42-6, LB15

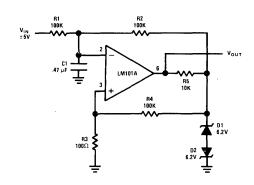

Programmable low-power: AN20-11, AN31-7

Protection: AN23-7 Regulation, load: AN1-5 Remote sensing: AN8-10

Ripple induced failures: AN23-7, LB10-2

Shunt regulator: AN8-1

Shutdown: AN8-4

Switching regulator (see Switching Regulator)

Temperature compensation: AN1-10, AN8-11, AN42-6, LB15

Transient response: AN1-6

POWER AMPLIFIER (see Buffer, High Current)

PREAMPLIFIER

Microphone, squelched: AN51-7 Phono: AN32-4, AN32-11 Servo: AN4-4, AN31-16 VOX: AN51-8

PROGRAMMABLE VOLTAGE REGULATOR: AN20-11, AN31-7

PULSE AMPLIFIER: AN8-11, AN13-4 PULSE REGULATOR: AN8-11 PULSE WIDTH MODULATOR: AN31-6 QUADRATURE OSCILLATOR: AN31-5, LB16 RECTIFIER, FAST HALF-WAVE: AN31-11, LB8-1 RECTIFIER, FULL-WAVE: AN20-8, LB8-2 REFERENCE VOLTAGE REGULATOR: AN20-6,

AN31-2, AN31-8

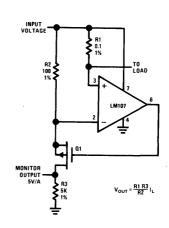

REMOTE SENSING

High current negative regulator: AN21-4 High negative voltage: AN21-9 Line resistance compensation: AN8-10

RECEIVER IF STRIP: AN6-5, AN15-2, AN15-5, LB13 RESET STABILIZED AMPLIFIER: AN20-7, AN38-4

**RESISTANCE MULTIPLICATION: AN29-14**

RF AMPLIFIER

AM/IF strip: AN15

Biasing: AN6-1

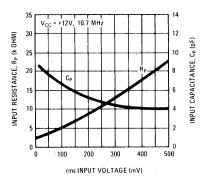

Cascode: AN6-1, AN6-3, AN6-4, AN32-9 Emitter coupled: AN6-1, AN6-2 Forward transadmittance: AN6-3

Gain: AN6-2

IF amplifier: AN6-5, AN15-2, AN15-5, LB13

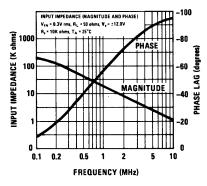

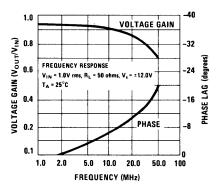

Input impedance: AN6-2, AN6-3 Tuned interstage circuits: AN6-4, LB13

RF OSCILLATOR (see Oscillator, RF)

RIPPLE, POWER SUPPLY: AN21-2, AN21-6, AN23-7, LB10-2

ROOT EXTRACTOR: AN4-6, AN31-18

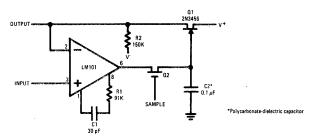

SAMPLE AND HOLD: AN4-3, AN5-8, AN29-6, AN31-12,

AN32-1, AN32-6, AN32-7. AN48-3, LB11-2

SCHMITT TRIGGER: AN32-12 SENSE VOLTAGE (see Current Limiting) SERVO PREAMPLIFIER: AN4-4, AN31-16

SETTLING TIME: LB17-2 SHUNT REGULATOR: AN8-1

SINE WAVE OSCILLATOR: AN20-9, AN29-9, AN31-5, AN31-6

AN31-7, AN32-7, AN32-8, AN51-8, LB16

SINGLE SUPPLY OPERATION: AN31-2, AN48-4

SLEW RATE: AN5-5, LB17 (see also Frequency Compensation,

Feedforward)

SOLAR CELL AMPLIFIER: AN4-5 **SQUARE ROOT CIRCUIT: AN4-6, AN31-18** SQUELCH AMPLIFIER, AGC: AN51 SQUELCH RELEASE TIMING: AN51-12

SQUELCHED PREAMPLIFIER: AN51-7

SSB

Demodulator: LB13-2 Modulator: AN8-6

SUMMING AMPLIFIER: AN20-3, AN31-1, AN31-13 SUPERHETERODYNE RECEIVER IF STRIP: AN15-5 SUPPLY VOLTAGE SPLITTING: AN31-2

SWITCH, ANALOG: AN5-8, AN28, AN32-4, AN32-8, AN32-9

AN32-10, AN32-12, AN33, AN38, AN53

SWITCHBACK CURRENT LIMITING (see Foldback Current

Limiting)

SWITCHING AND LINEAR REGULATOR COMBINATION: AN2-11

SWITCH CURRENT REGULATOR: AN8-4

SWITCHING REGULATOR

Capacitor selection: AN21-11 Catch diode selection: AN21-11 Current limiting: AN2-8, AN8-4, AN21-12

Dissipation: AN21-11

Driven: AN2-7, AN21-14

Efficiency: AN2-5, AN2-6, AN2-7, AN21-10

Frequency of operation: AN2-4, AN2-5, AN2-6, AN2-7 High negative current: AN21-11, AN21-12, AN21-13

#### SUBJECT INDEX (cont'd)

High positive current: AN1-11, AN2-6, AN8-2,

High voltage: AN2-11 Hints: AN21-11

Inductor core selection: AN21-11

Line regulation: AN2-6, AN21-11

Modulation: AN8-6

Negative: AN2-10, AN21-10, AN21-11, AN21-12, AN21-13

Overload shutdown: AN8-2, AN21-13 Overvoltage protection: AN8-3 Ripple: AN2-4, AN21-11 Self-oscillating: AN2-2, AN21-10 Shutdown: AN8-2, AN21-13 Symmetrical: AN2-10 Synchronous: AN2-7, AN21-14 Theory: AN1-11, AN2-2, AN21-10

SYMMETRICAL SWITCHING VOLTAGE REGULATOR: AN2-10

#### SYMMETRICAL VOLTAGE REGULATOR

LM100 as a symmetrical regulator: AN1-9

Regulation: AN21-6

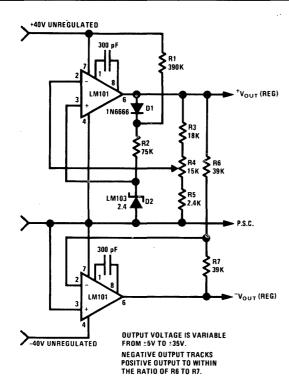

Tracking regulator: AN20-10, AN21-6, LB7

TEMPERATURE COMPENSATION (see Drift Compensation)

TEMPERATURE CONTROLLER: AN8-5

TEMPERATURE PROBE AMPLIFIER: AN31-17

TEST SET, OPERATIONAL AMPLIFIER: AN24

THRESHOLD DETECTOR: AN20-10, AN31-3

TIME DOMAIN MULTIPLEXING: AN53-1

TIMER, INTERVAL: AN31-17

TONE CONTROL: AN32-3, AN32-11

TRACKING VOLTAGE REGULATOR: LB7 (see also Symmetrical

Voltage Regulators)

TRANSADMITTANCE, RF AMPLIFIER: AN6-3

TRANSFER FUNCTION TEST SET: AN24-4

TRIANGLE WAVE OSCILLATOR: AN20-10, AN24-6, AN31-6

TRIGGER, SCHMITT: AN32-12

TUNED RF CIRCUITS (see RF Amplifiers)

UNITY-GAIN BUFFER: AN20-2

#### **VOLTAGE COMPARATOR**

Analog to Digital converter circuit: LB6-1

AC coupled: LB6-2

Buffered output: AN29-15

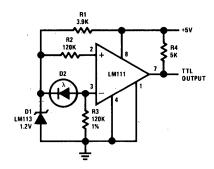

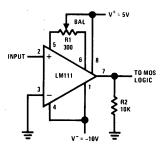

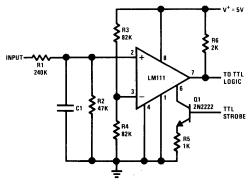

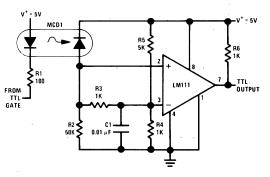

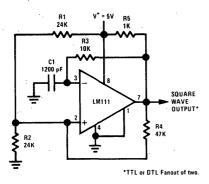

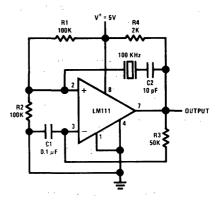

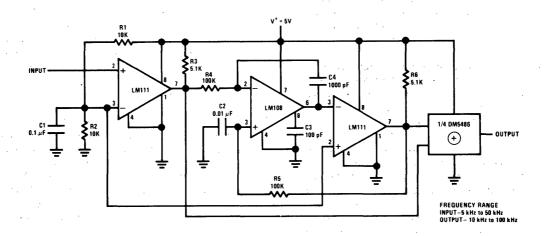

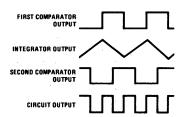

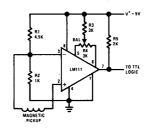

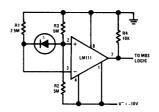

Circuit description: LM111/LM211/LM311: AN41-1, LB12

Comparison: LB12-2

DTL driver: AN4-2, AN10-2, AN29-15, AN31-3, LB12-2

Dual limit, high speed: AN48-3

Fast: LB-6 FET: AN34-2 Hints: AN41-5

Lamp driver: AN4-2, LB12-2

MOS driver: AN10-2, AN41-2, AN41-3, LB12-2

Op. amp. voltage comparator: AN4-2

TTL driver: AN4-2, AN10-2, AN29-15, AN31-3, AN41-2,

AN41-3, LB12-2

Zero crossing: AN31-17, AN41-2, AN41-3, LB6-2, LB12-2

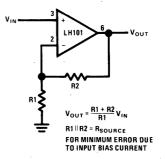

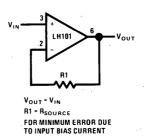

#### VOLTAGE FOLLOWER

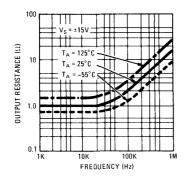

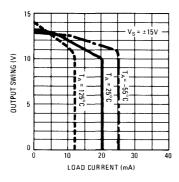

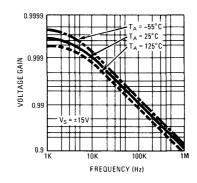

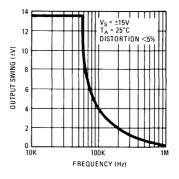

A to D ladder driver: AN5-7 Bandwidth, full power: AN5-5 Bias current: AN5-3, AN20-3 Buffer, voltage reference: AN5-7 Circuit description LH0033: AN48-1

Circuit description LM102/LM202/LM302: AN5-1 Circuit description LM110/LM210/LM310: LB11

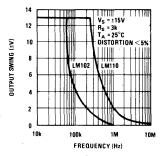

Clamping, input: AN5-6 Comparison: LB11-2 Frequency response: AN5-3

Gain: AN5-5

Hints, operating: AN5-6, AN20-2 Increased output swing: AN5-5 Offset adjustment: AN31-4, LB9-2 Resistance, output: AN5-5

Slew rate: AN5-5

Source resistance effect: AN5-5 Transient response: AN5-7

Voltage reference: AN20-6, AN31-2, AN31-8

Voltage reference buffer: AN5-7

VOLTAGE REGULATOR (see Positive, Negative, or Switching

Voltage Regulator)

VOLTMETER, FETVM: AN32-2

VOX PREAMPLIFIER: AN51-8

WEIN BRIDGE OSCILLATOR: AN20-9, AN31-6, AN31-7

AN32-7, AN51-8

WINDOW DISCRIMINATOR, MULTIPLE APERTURE: AN31-3 ZERO CROSSING DETECTOR: AN31-17, AN41-2, AN41-3

LB6-2, LB12-2

A VERSATILE, MONOLITHIC VOLTAGE REGULATOR

A VERSATILE, MONOLITHIC VOLTAGE REGULATOR

#### INTRODUCTION

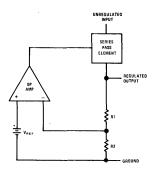

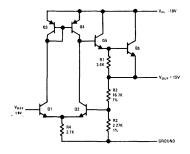

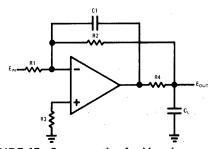

The great majority of linear integrated circuits being produced today are DC amplifiers, particularly operational amplifiers. This has come about both because the DC operational amplifier is a basic analog building block and because this device makes good use of the well-matched characteristics of monolithic components, characteristics which are normally expensive to duplicate with discrete parts. A voltage regulator is a circuit which requires similar precision. As shown in the diagram of Figure 1, a basic regulator circuit employs an operational amplifier to compare a reference voltage with a fraction of the output voltage and control a series-pass element to regulate the output.

FIGURE 1. Basic Series-Regulator Circuit

Perhaps the reason that monolithic regulators have not appeared sooner is because it is difficult to make one design flexible enough to satisfy an appreciable percentage of the market. Different systems require vastly different output voltages and currents, as well as varying degrees of regulation. In addition, the current handling ability of monolithic circuits is limited because of the large physical die size of high-current transistors. Power dissipation is also a factor, since there are no readily available multi-lead power packages for integrated circuits.

A design is presented here which is versatile enough to overcome many of these problems. It is able to deliver regulated voltages which are externally adjustable from 2V to 30V, operating as either a linear, dissipating regulator or a high efficiency switching regulator. This covers the range from low-level logic circuits to the majority of solid-state linear systems. Although the output current of the integrated circuit is limited (12 mA), an external transistor can be added for currents

to 250 mA. A second external power transistor will enable the regulator to deliver currents in excess of 2A.

The regulation is better than 1-percent for widely varying load and line conditions. The device also features 1-percent temperature stability over the full military temperature range, externally adjustable short-circuit-current limiting, fast response to both load and line transients, a small standby power dissipation, freedom from oscillations with varying resistive and reactive loads, and the ability to self start with any load.

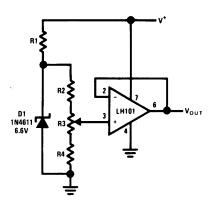

#### **VOLTAGE REFERENCE**

The voltage reference of a regulator is normally a temperature compensated avalanche diode. Commercially available diodes have a breakdown voltage temperature coefficient of 0.01-percent/°C to 0.0005/°C, depending on selection. Normal integrated circuit processing yields an avalanche diode with acceptable characteristics for this application. The reversed-biased emitter-base junction of the transistors has a breakdown voltage of approximately 6.5V and an unusually uniform temperature coefficient of +2.3 mV/°C. Hence, the positive temperature coefficient of the avalanche diode can be very nearly balanced out by a forward biased, diode-connected transistor to produce a temperature compensated reference. However, exact compensation requires surface impurity concentrations in the transistor-base diffusion which are higher than desired to produce optimized transistors. One design objective of an integrated regulator is, then, to develop a reference element which permits nearly-exact compensation without requiring process alteration.

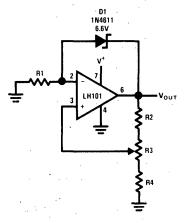

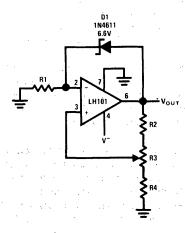

Another design objective is also centered around the reference. In the regulator circuit of Figure 1, the output voltage can be adjusted down to, but not lower than, the reference voltage. This means that, unless additional circuitry is incorporated, the reference restricts the use of the regulator to applications requiring output voltages above about 8V. It is therefore desirable to obtain as low as possible a reference voltage.

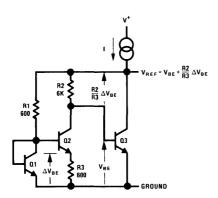

A circuit which provides a simple solution to the temperature compensation problem in addition to supplying a low reference voltage is shown in Figure 2. In this circuit, the breakdown diode is supplied by a current source from the unregulated supply. An emitter follower, Q<sub>1</sub>, buffers the output voltage of the diode. The positive temperature coefficient of this buffered output is increased to approximately 7 mV/°C by the addition of the diode connected transistor, Q<sub>2</sub>

A resistor divider reduces this voltage as well as the temperature coefficient to exactly compensate for the negative temperature coefficient of  $\mathbf{Q}_3$ , producing a temperature compensated output. With the integrated circuit process used, this output voltage is about 1.8V for optimum compensation.

FIGURE 2. Voltage Reference Circuitry

One feature of this integrated reference is that the reverse emitter base breakdown, must have an extremely sharp knee (even in the 1  $\mu$ A region) in order for the transistors in the circuit to be acceptable. Therefore, the diodes can be reliably operated at low currents where the noise is low and has a nearly uniform frequency spectrum. At higher currents (above about 100  $\mu$ A for these particular devices) the noise becomes a sensitive function of current with low-repetition-rate pulsations. At even higher currents, the noise reduces in amplitude and loses its current sensitivity but still retains a heavy fluctuation component.

#### REGULATOR CIRCUIT

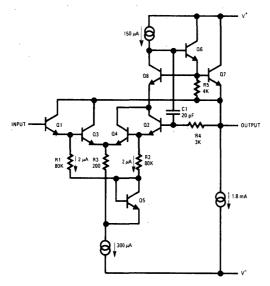

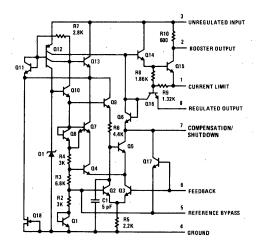

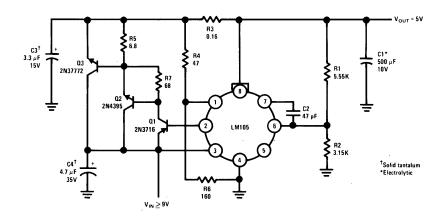

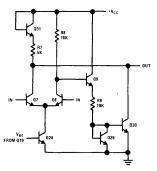

A simplified schematic of the regulator is shown in Figure 3. It is a single-stage differential amplifier with a Darlington, emitter-follower output.

FIGURE 3. Simplified Schematic of the Regulator

The gain of this stage is made much higher than would normally be expected by the use of  $\Omega_3$  and  $\Omega_4$  as collector loads. If very large PNP current gain and good matching are assumed, the collector current of  $\Omega_1$ . Therefore, the differential stage will be in balance independent of the magnitude of the collector currents of  $\Omega_1$  and  $\Omega_2$  and for the complete range of output voltage settings and input voltage variations. Even this simple circuit gives a no load to full load regulation of 0.2-percent and a line regulation of 0.05-percent per volt.

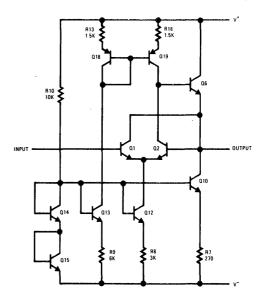

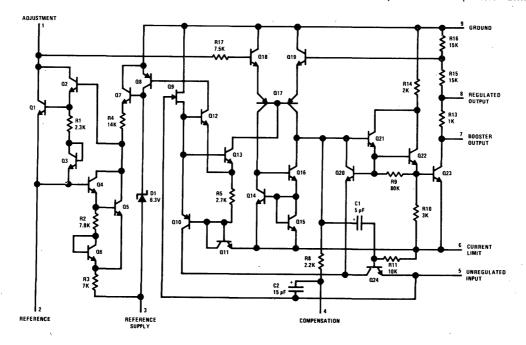

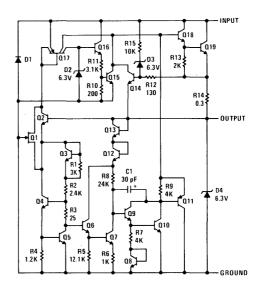

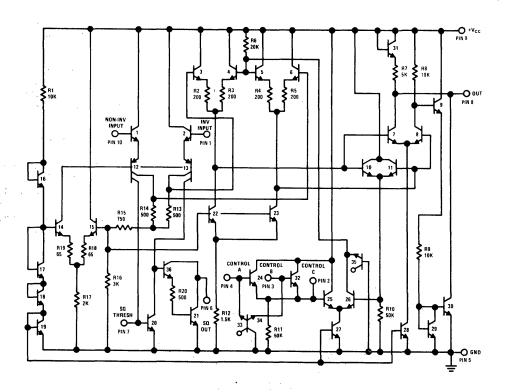

The complete schematic of the regulator in Figure 4 shows several additions. First, an emitter follower,

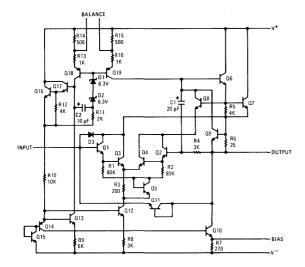

FIGURE 4. Complete Schematic of the LM100

${\rm Q_3}$ , and a level-shifting diode,  ${\rm Q_1}$ , have been added to increase the effective current gain of the PNP transistor,  ${\rm Q_2}$ . This device is a lateral PNP which has a low current gain (0.5 to 5) but has the advantage that it can be made without adding any steps or process controls to the normal NPN integrated circuit process. One collector of the PNP serves as a collector load for the error-sensing transistor,  ${\rm Q_9}$ . A second collector supplies current for the breakdown diode,  ${\rm D_1}$ . A third collector, which determines the output current of the other two, maintains a current nearly equal to the collector current of  ${\rm Q_4}$  by means of negative feedback to the PNP base through  ${\rm Q_3}$  and  ${\rm Q_1}$ .

The collector current of  $Q_4$  is established at a known fraction of the resistive divider current through  $R_1$  and  $R_2$  by the second emitter on  $Q_5$ . This emitter-base junction of  $Q_5$ , which is five times larger than that of  $Q_6$ , bypasses most of the divider current, at a ratio determined by the relative geometries, to the collector of  $Q_5$ . This current, combined with the collector current of  $Q_8$  through the other emitter of  $Q_5$ , supplies current for the emitter of  $Q_3$  to drive the base of  $Q_2$ .

$R_4$  and  $R_9$  serve the sole purpose of starting the regulator. They only need to supply enough base current to  $Q_2$  to bring the breakdown diode,  $D_1$ , up to voltage. Since it can supply many times the required current under worst-case conditions, starting is ensured.

The clamp diode,  $D_2$ , reduces the current variation seen by  $Q_3$  with changes in input voltage, improving line regulation.  $R_9$  is a pinch resistor which has a sheet resistivity more than two orders of magnitude higher than diffused base resistors, so it can be made quite small physically. Pinch resistors do have the disadvantages of non-linear voltage-current characteristic, a large temperature coefficient, a low breakdown voltage and rather large production variations in sheet resistivity. However, as shown in Reference 3, these characteristics can be designed around and actually put to good use, as they are here.

The start-up network is connected to the regulator output terminal, rather than ground, so that the internal power dissipation is minimized without requiring large resistance values. Because of this, the load current of the regulator cannot drop below the current supplied from the unregulated input through  $R_{\rm d}.$  If it does, the circuit will no longer regulate. This is not usually a problem, since the resistive divider which sets the output voltage will normally draw enough current. However, it should be kept in mind in applications where the regulator might be lightly loaded and the difference between the unregulated input voltage and the regulated output voltage is apt to be high.

The collector of the output transistor,  $Q_{12}$ , is brought out separately to permit the addition of an external PNP transistor for higher currents. An emitter-base resistor for the external PNP,  $R_8$ , is also included. This resistor is shorted out when the regulator is used without the external transistor.

The output of the voltage reference is brought out so that the inherent noise of the breakdown diode can be bypassed out. Since the low operating current of the diode minimizes low-frequency noise, adequate bypassing can be provided by a capacitor as small as  $0.1~\mu F$ .

The purpose of the clamp diode,  $D_3$ , is to keep  $O_9$  from saturating when the circuit is used as a switching regulator. It plays no functional role in linear operation.

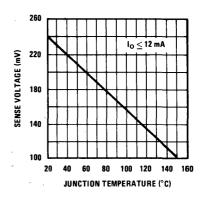

Output-current limiting is provided by  $Q_{10}$ . The value of current limit is determined by an external resistor between the current limit, and regulated output terminals. When the voltage drop across this resistor becomes high enough to turn on

$Q_{10}$ , it removes base drive from  $Q_{11}$  to prevent any further increase in output current. It can be seen from Figure 4 that the voltage turning on Q10 is the voltage drop across the external current limit resistor plus a fraction of the emitterbase voltage of the series pass transistor,  $Q_{12}$ . This arrangement was used for two reasons. First, less voltage is dropped across the current limit resistor, permitting the circuit to regulate with lower input voltages. Second, since in current limit Q<sub>12</sub> is operated at a much higher emitter-current density than is Q10, it has a lower negative temperature coefficient of emitter-base voltage. The negative temperature coefficient of the emitter-base voltage of Q10 along with this difference in temperature coefficients causes the current limit to decrease by a factor of 2 as the chip temperature increases from 25°C to 150°C. This enables the regulator to deliver maximum current to room temperature but still be protected when the output is shorted and the dissipation increases: the current will decrease as the chip heats, holding the dissipation to a safe level.

It is interesting to note that this current limit scheme will only work when the two transistors are in close thermal contact, as they are in a monolithic integrated circuit.

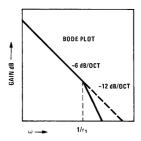

Since a regulator is an operational amplifier with a large amount of feedback, frequency compensation is required to prevent oscillations. However, a voltage regulator has compensation problems in addition to those encountered in an operational amplifier. For one, the compensation method must provide a high degree of rejection to input voltage transients. Secondly, it must be stable with reactive loads which are far heavier than those normally encountered with operational amplifiers. Thirdly, it must minimize the overshoot caused by large load and line transients.

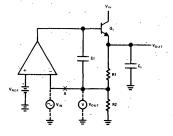

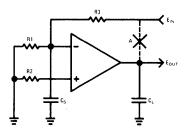

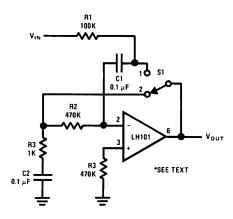

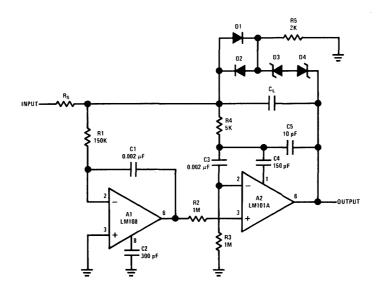

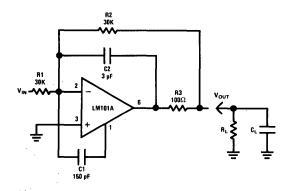

A compensation method satisfying those requirements is shown in Figure 5. The operational amplifier is connected as an integrator and isolated

FIGURE 5. Simplified Schematic Showing Regulator Frequency Compensation

from the load with an emitter follower, which serves as a series pass transistor. If the feedback loop is opened at point A and the frequency response measured, it can be seen that the feedback at high frequencies where the loop response must be controlled is through  $C_F$ . Reactive loads have little effect since they are isolated from the high frequency feedback path by  $Q_5$ .

This compensation method provides excellent response to load transients. That part of a load transient which is not absorbed by the output capacitor,  $C_L$ , sees the output impedance of  $Q_5$  which is quite low since it is driven by an operational amplifier with a low AC output impedance.

In the actual regulator (Figure 4) the operational amplifier is a single stage amplifier ( $Q_9$ ). Hence, it is stable in the integrator connection, with a collector base capacitor on  $Q_9$ , without additional compensation which might degrade either the load or line transient response. The series pass transistor is a compound emitter follower to insure isolation from reactive loads. In addition, the stability of the circuit is not dependent on the output impedance of the unregulated supply. It is also stable with no bypass capacitance on the output (if external booster transistors are not used) so it is possible to obtain extremely rapid current limiting as might be required with sensitive transistor loads.

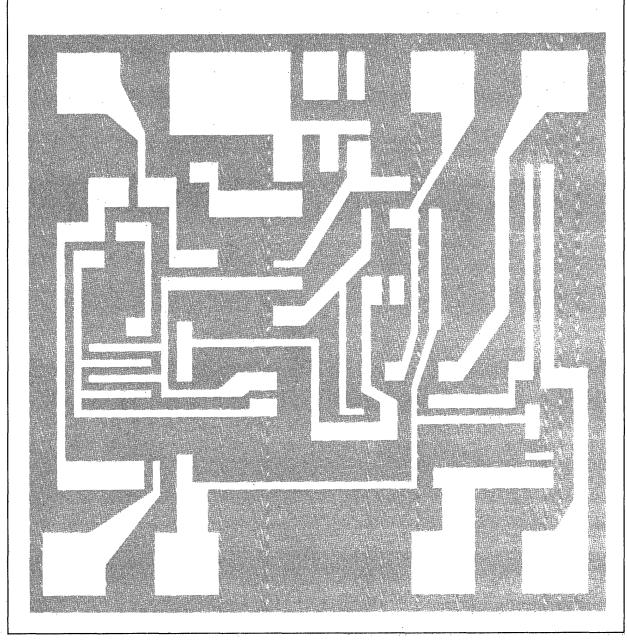

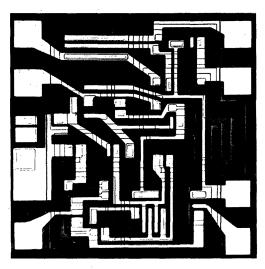

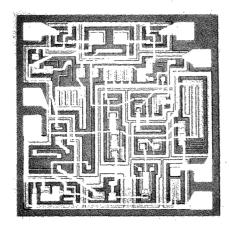

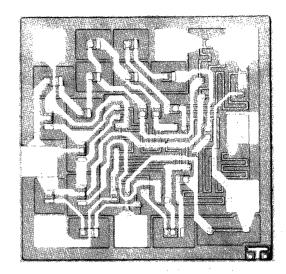

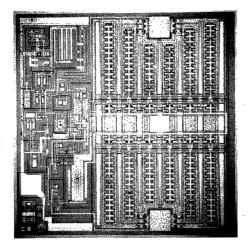

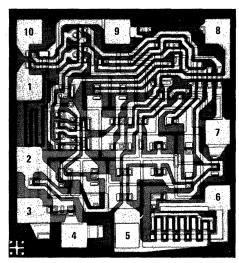

A photomicrograph of the monolithic regulator die is shown in Figure 6. Since the design requires a minimum of resistance, substituting active devices where possible, the entire circuit has been constructed on a 38-mil-square die. This die size is comparable to that of a single silicon transistor.

FIGURE 6. Photomicrograph of the LM100 Regulator

#### **APPLICATIONS**

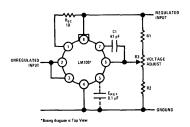

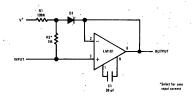

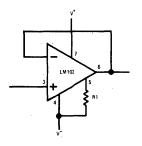

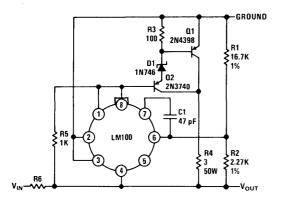

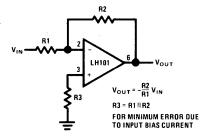

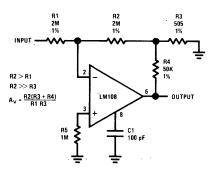

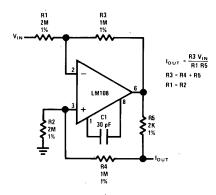

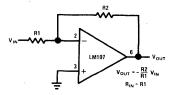

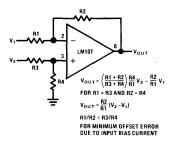

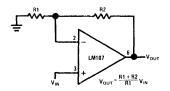

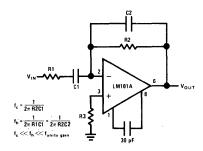

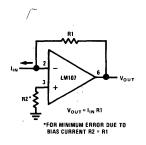

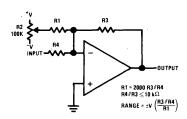

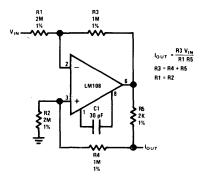

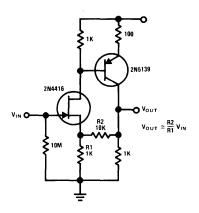

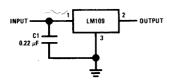

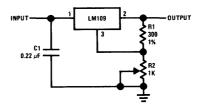

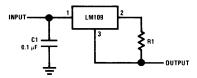

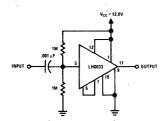

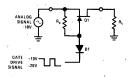

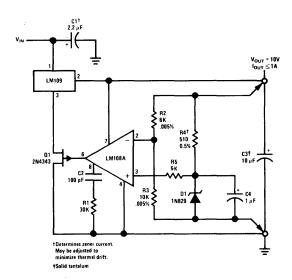

The basic regulator circuit for the LM100 is shown in Figure 7. The output voltage is set by  $R_1$  and

FIGURE 7. Basic Regulator Circuit

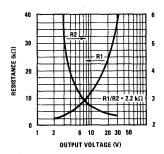

R<sub>2</sub>, with a fine adjustment provided by the potentiometer, R<sub>3</sub>. The resistance seen by the feedback terminal should be approximately 2.2k to minimize drift caused by the bias current on this terminal. Figure 8 is based on this and gives the optimum

FIGURE 8. Optimum Divider Resistance Values as a Function of Output Voltage

values for  $R_1$  and  $R_2$  as a function of design-center output voltage. The potentiometer should be least 1/4 of  $R_2$  to insure that the output can be set to the desired voltage.

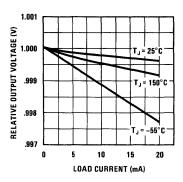

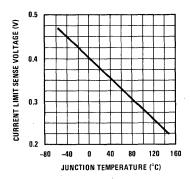

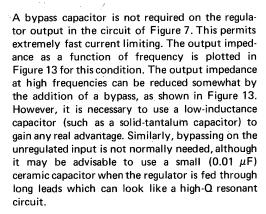

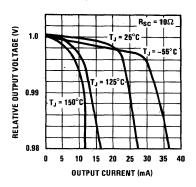

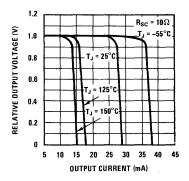

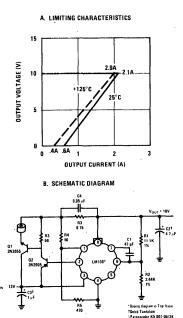

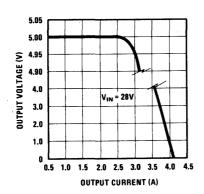

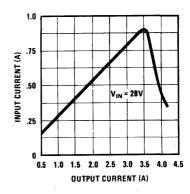

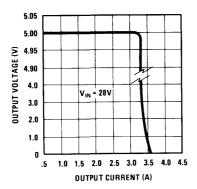

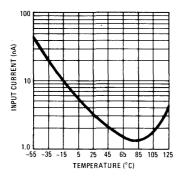

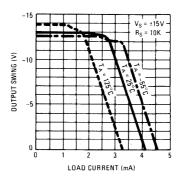

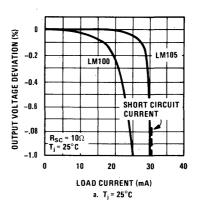

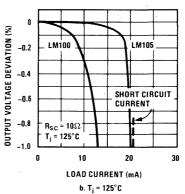

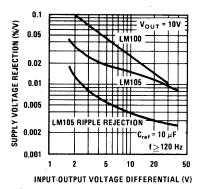

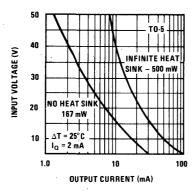

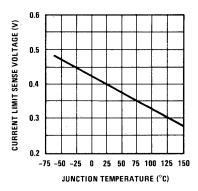

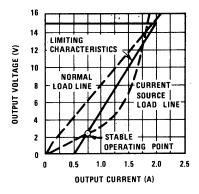

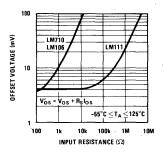

It is possible to operate the regulator with or without internal current limiting. If current limiting is not needed, improved load regulation can be realized by shorting together the current limit terminals (R<sub>SC</sub> = 0). Figure 9 gives the load regulation for this condition. Short circuit protection is obtained by connecting a resistor between the current limit terminals. The resistor value is determined from the current limit sense voltage which is plotted as a function of temperature in Figure 10. for low output currents which corresponds to the case where external booster transistors are used. The current limit sense voltage is the voltage across the current limit terminals when the regulator is current limiting with the output shorted. The regulation and current limit characteristics with a  $10\Omega$  current limit resistor are given in Figures 11 and 12, respectively.

FIGURE 9. Regulation Characteristics Without Current Limiting

FIGURE 10. Current Limit Sense Voltage as a Function of Junction Temperature

A reduction in the output noise can be realized

FIGURE 11. Regulation Characteristics with Current Limiting

FIGURE 12. Current Limiting Characteristics

by the addition of a 0.1  $\mu F$  capacitor on the reference bypass terminal. This reduces the noise inherent in the reference diode.

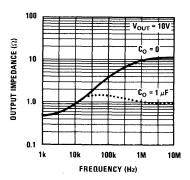

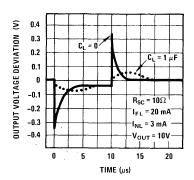

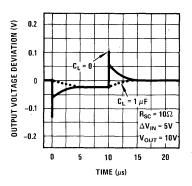

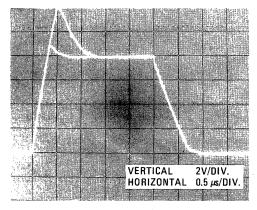

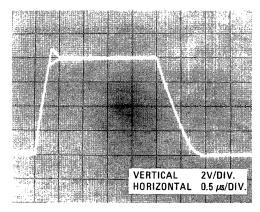

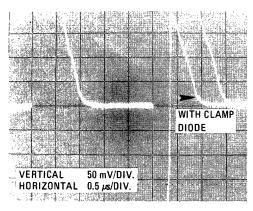

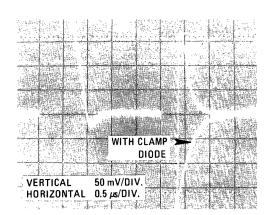

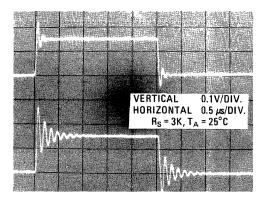

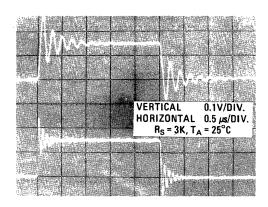

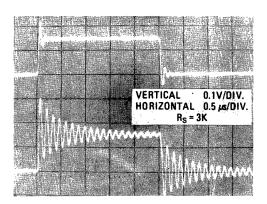

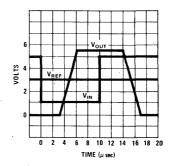

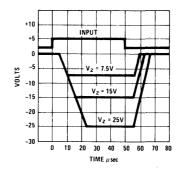

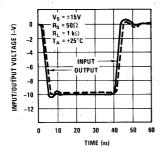

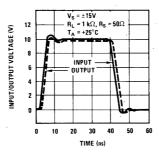

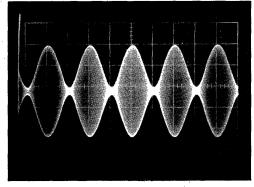

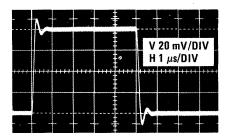

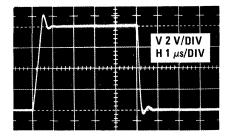

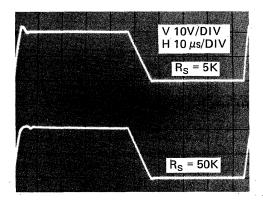

The transient response of the regulator is shown in Figures 14 and 15. Figure 14 shows the response to a current step from 3 mA to 15 mA, without any output bypass capacitor and with a  $10\Omega$  current limit resistor. The overshoot can be reduced both by the addition of an output bypass capacitor and by the removal of the current limit resistor since the overshoot is developed across the resistor. The response to a line voltage transient is shown in Figure 15. Neither the line transient response nor the load transient response is affected by the output voltage setting. Therefore, the overshoot becomes a smaller percentage of the output voltage as this voltage is increased.

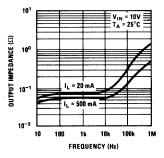

FIGURE 13. Output Impedance as a Function of Frequency

FIGURE 14. Load Transient Response

The regulator provides a line regulation of 0.1-percent per volt change in input voltage. The full-load regulation is better than 0.5-percent. The output voltage drift is less than 1-percent for a temperature change from +25°C to either the -55°C or +125°C temperature extreme. The regulator will operate within specifications for output voltages between 2V and 30V, for input voltages between 8.5V and 40V, for a difference between the input and output voltage between 3V and 30V and over -55°C to +125°C temperature range. This applies whether the regulator is used alone or with external current-boosting transistors.

The load and line regulation given above is for a constant chip temperature on the integrated circuit. Temperature drift effects caused by internal heating must be taken into account separately

FIGURE 15. Line Transient Response

when the device is operated under conditions of high dissipation.

#### **HIGH POWER REGULATORS**

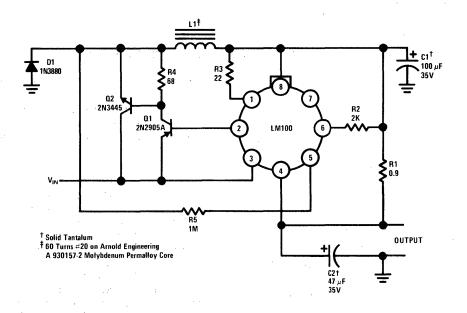

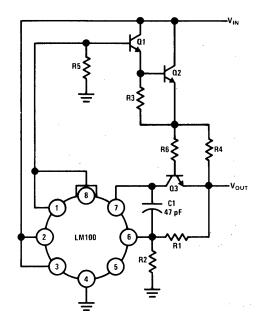

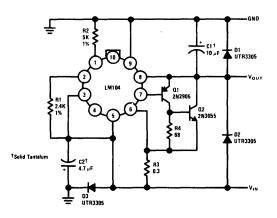

Increased output current capability and improved load regulation can be obtained by the addition of external transistors. The output currents achievable are in fact limited only by the power dissipating and current handling capabilities of the external transistors. The use of these external transistors as the series pass elements also reduces internal dissipation in the integrated circuits and prevents the temperature drift mentioned above.

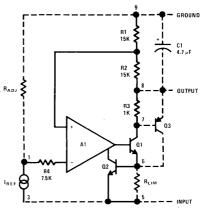

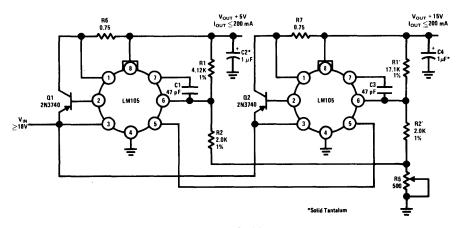

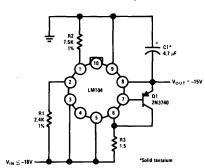

One circuit which is capable of up to 200 mA load current with 1-percent regulation is shown in Figure 16. The load characteristics are essentially the same as those given in Figures 11 and 12 except that the current scale is multiplied by a factor of 10.

FIGURE 16. Regulator Connected for 200 mA Output Current

When external transistors are used, it is necessary to bypass the output terminal close to the integrated circuit. This is required to suppress oscillations in the minor feedback loop around the external transistor and the output transistor of the integrated circuit ( $Q_{12}$  in Figure 4). Since the instability is inclined to occur at high frequencies, a low inductance (solid tantalum) capacitor must be used. Electrolytic capacitors which have a high equivalent series resistance at high frequencies are not effective.

It is not always necessary to bypass the input of the regulator in Figure 16, although it would be advisable if the regulator were being operated from long supply leads or from a source with unknown output impedance characteristics. Again, if a bypass is used, it should be of the low-inductance variety and located close to the regulator.

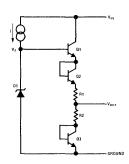

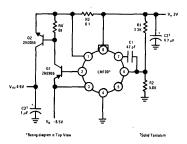

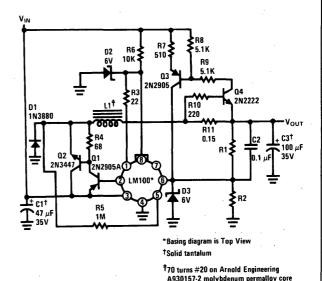

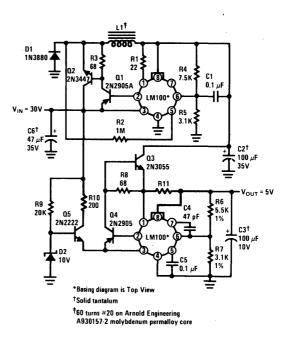

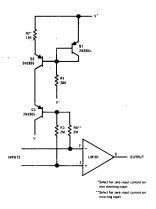

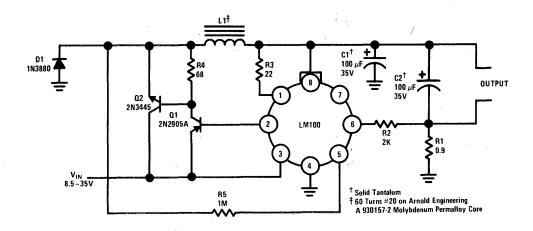

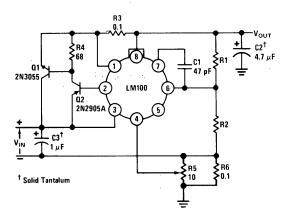

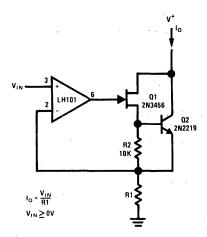

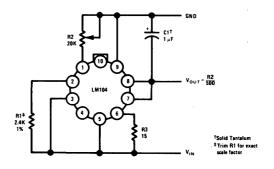

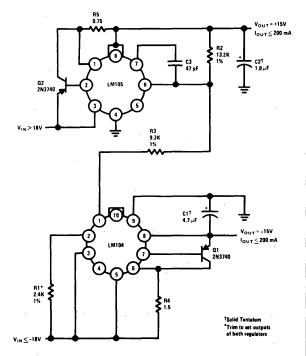

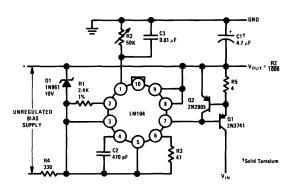

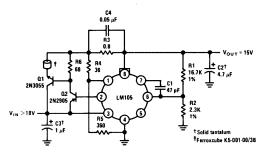

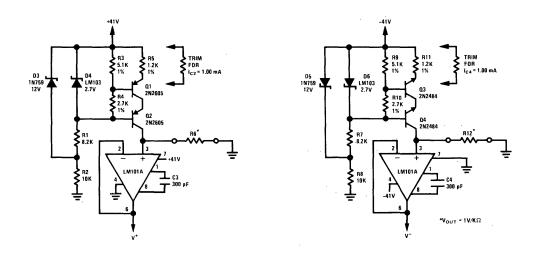

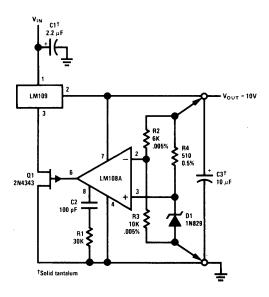

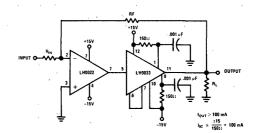

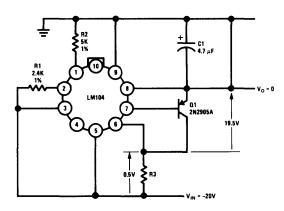

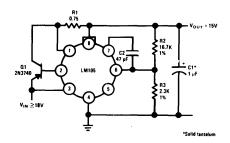

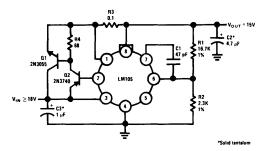

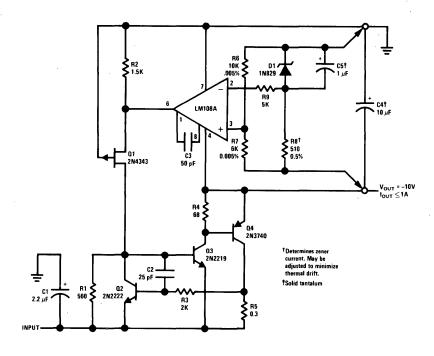

If output currents much greater than about 200 mA are required, it becomes necessary to add a second external transistor to provide more current gain. The method of accomplishing this is shown in Figure 17. The PNP transistor,  $\Omega_2$ , is used to drive

FIGURE 17. Regulator Connected for 2A Output Current

a NPN power transistor,  $Q_1$ . With this circuit it is necessary to bypass both the input and output terminals of the regulator, as indicated, with low inductance capacitors to prevent oscillation in the minor feedback loop through  $Q_2$ ,  $Q_1$  and the output transistor of the integrated circuit. In addition, with certain types of NPN power transistors, it may be necessary to install a ferrite bead<sup>4</sup> in the emitter lead of the device to suppress parasitic oscillations in the power transistor.

The load characteristics of the circuit are again essentially the same as those given in Figures 11 and 12 except that the current scale is multiplied by a factor of 100. As before, the line regulation, temperature drift, etc., are all the same as for the basic regulator.

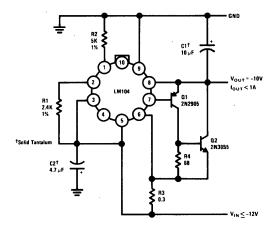

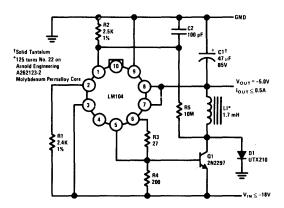

Another high-power regulator is shown in Figure 18. This circuit is a minor variation of that described previously and is useful when low output voltages

FIGURE 18. Circuit for Obtaining Higher Efficiency Operation with Low Output Voltages

are required. Here, the series pass transistor,  $Q_2$ , and the regulator are operated from separate supplies. The series pass transistor is run off of a low voltage main supply which minimizes the input-output differential for increased efficiency. The regulator, on the other hand, operates from a low power bias supply with an output greater than 8.5 V.

With this circuit, care must be taken that  $\Omega_2$  never saturates. Otherwise,  $\Omega_1$  will try to supply the entire load current and destroy itself, unless the bias supply is current limited.

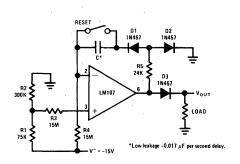

#### SWITCHBACK CURRENT LIMITING

With high power regulators it is possible to run into excessive power dissipation when the output is shorted, even though the regulator has current limiting. This happens, with normal current limiting, because the series pass transistor must dissipate the power generated by the full input voltage at a current slightly above the full load current. This dissipation can easily be three times the worst case dissipation in normal operation at full load.

This problem can be overcome by reducing the short circuit current to a value substantially less than the full load current. A circuit for doing this with the LM100 is shown in Figure 19, along with the current limit characteristics obtained. As can be seen from the schematic, two components are added to achieve this —  $\rm R_4$  and  $\rm R_5$ . These resistors supply a voltage which bucks out the voltage drop across the current limit sense resistor,  $\rm R_3$ , thereby increasing the maximum load current from 0.5A to 2.0A. When the output is shorted, however, this bucking voltage is no longer generated so the short circuit current is only 0.5A.

FIGURE 19. Circuit for Obtaining Switchback Current Limiting with the LM100

In this circuit, the voltage drop across the currentsense resistor at full load is 1.5V as compared to about 0.37V when the bucking arrangement is not used. However, this does not increase the minimum input-output voltage differential since the output of the LM100 does not see this increased voltage. With a 10V output and a 2A load, the circuit will still work with input voltages down to 13V, worst case.

In addition to providing the switchback characteristics,  $\rm R_4$  and  $\rm R_5$  also give a 20 mA preload on the regulator so that it can be operated without a load.

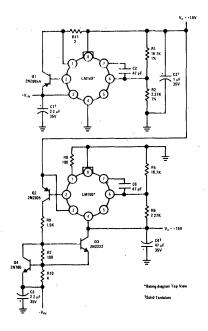

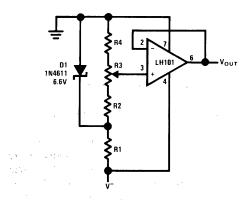

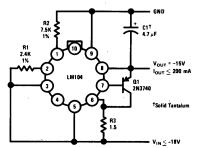

#### **NEGATIVE VOLTAGE REGULATORS**

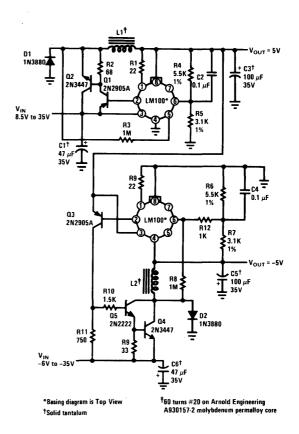

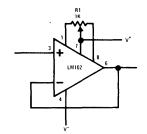

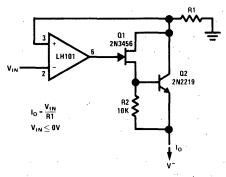

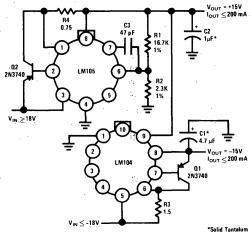

A schematic diagram for using the LM100 as both a positive and a negative regulator is shown in Figure 20. With this circuit, the inputs and outputs of both regulators have a common ground.

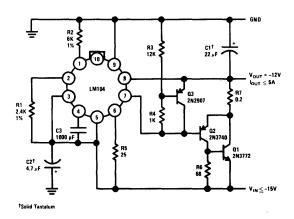

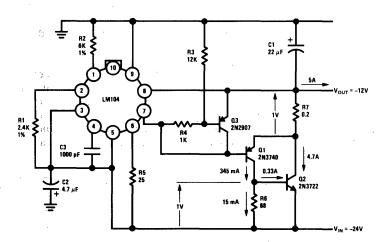

The positive regulator is identical to those described previously. For the negative regulator, the normal output terminal (pin 8) of the LM100 is grounded, and the ground terminal (pin 4) is connected to the regulated negative output. Hence, as in the usual mode of operation, it regulates the voltage between the output and ground terminals. A PNP booster transistor,  $\mathbf{Q}_2$ , is connected in the normal manner; and it drives a NPN series-pass transistor,  $\mathbf{Q}_3$ . The additional components ( $\mathbf{R}_7$ ,  $\mathbf{R}_8$ ,  $\mathbf{R}_9$ ,  $\mathbf{R}_{10}$  and  $\mathbf{Q}_4$ ) are included to provide current limiting.

FIGURE 20. Positive and Negative Regulators using the LM100

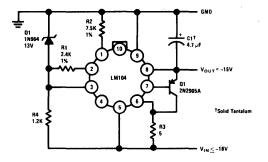

Figure 21 shows a somewhat simpler circuit. Split secondaries are used on a power transformer to create a floating voltage source for the negative regulator. With this floating source, the conventional regulator is used, except that the output is grounded.

FIGURE 21. Circuit for using the LM100 as Both a Positive and a Negative Regulator

#### TEMPERATURE COMPENSATING REGULATORS

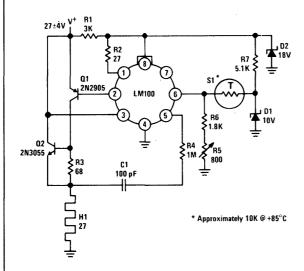

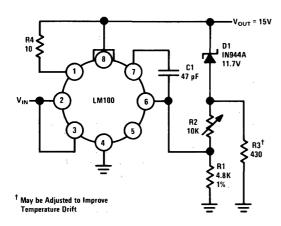

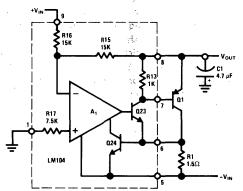

In the majority of applications, it is desired that the output voltage of the regulator be constant over the operating temperature range of equipment. However, in some applications, improved performance can be realized if the output voltage of the regulator changes with temperature in such a way as to operate the load at its optimum voltage.

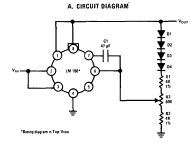

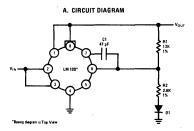

An example of this in integrated logic circuitry. Optimum performance can be realized by powering the devices with a voltage that decreases with increasing temperature. A circuit which does this is shown in Figure 22. Silicon diodes are used in

B. OUTPUT VOLTAGE AS A FUNCTION OF TEMPERATURE

FIGURE 22. Temperature Compensating Voltage

Regulator with Negative Temperature

Coefficient

the feedback divider to give the required negative temperature coefficient. The advantage of using diodes, rather than thermistors or other temperature sensitive resistors, is that their temperature coefficient is quite predictable so it is not necessary to make cut-and-try adjustments in temperature testing. Reference 6 gives a method of predicting the voltage change in the emitter base voltage of a transistor within 5 mV over a 100°C temperature change. Diodes are not quite this predictable, but diode connected transistors (base shorted to collector) can be used if greater accuracy is required.

#### **SWITCHING REGULATORS**

The dissipating-type regulators described already

have the advantages of fast response to load transients as well as low noise and ripple. However, since they must dissipate the difference between the unregulated supply power and the output power, they sometimes have a low efficiency. This is not always a problem with AC line-operated equipment because the power loss is easily afforded, because the input voltage is already fairly well regulated, and because losses can be minimized by adjustment of transformer ratios in the power supply. In systems operating from a fixed DC input voltage, the situation is often much different. It might be necessary to regulate a 28V input voltage down to 10V. In this case the power loss can quickly become excessive. This is true even if efficiency is not one of the more important criteria, since the high power dissipation requirements will necessitate expensive power transistors and elaborate heat sinking methods.

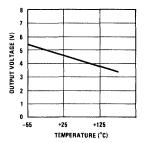

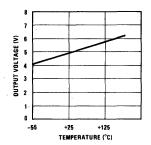

B. OUTPUT VOLTAGE AS A FUNCTION OF TEMPERATURE

FIGURE 23. Temperature Compensating Voltage Regulator with Positive Temperature Coefficient

One way of overcoming this difficulty is to go to a switching regulator. With switching regulators, efficiencies approaching 90-percent can be realized even though the regulated output voltage is only a fraction of the input voltage. By proper design, transient response and ripple can also be made quite acceptable.

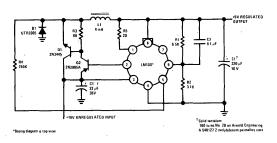

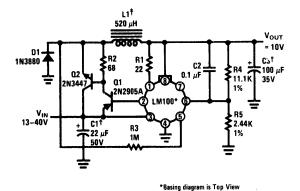

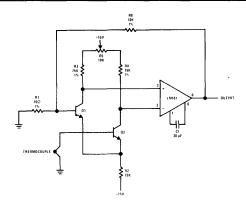

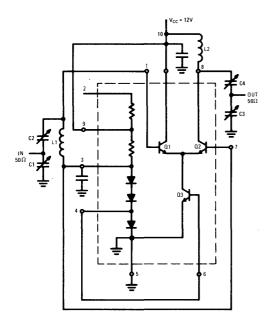

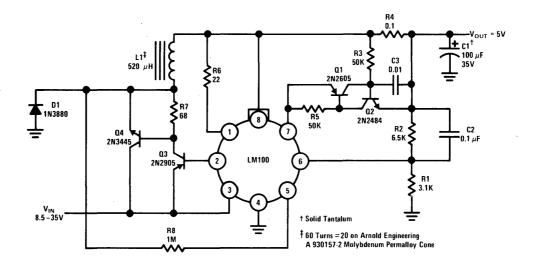

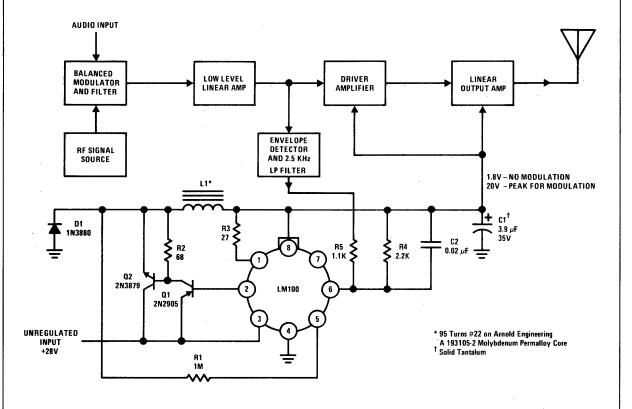

A circuit using the LM100 as a switching regulator is given in Figure 24. It is designed for an application where a 28V DC power source must supply a system operating at 10V.

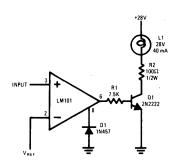

As shown in Figure 24, the LM100 is connected in much the same way as a linear regulator when

FIGURE 24. High Current Switching Regulator

it is used as a switching regulator. Two external transistors, a NPN and a PNP, are connected in cascade to handle the output current. The regulated output is fed back through a resistive divider which determines the output voltage in the normal manner. The regulator is made to oscillate by applying positive feedback to the reference terminal through R<sub>4</sub> (from Figure 4, the reference terminal is the non-inverting side of the input differential amplifier).

In operation, the switching transistors,  $Q_1$  and  $Q_2$ , turn on when the voltage on the feedback terminal is less than that on the reference terminal. This action raises the reference voltage since current is fed into this point from the switch output through  $R_4$ . The switching transistors remain on until the voltage on the feedback terminal increases to the higher reference voltage. The regulator then switches off, lowering the reference voltage. It remains off until the voltage on the feedback terminal falls to the lower reference voltage.

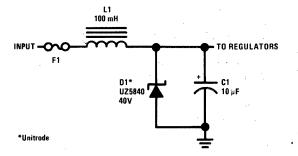

When the switch transistors are on, power is delivered from the power source to the load through  $L_1$ . When the transistors turn off, the inductor continues to deliver current to the load with  $D_1$  supplying a return path. Since fairly fast rise and fall times are involved,  $D_1$  cannot be an ordinary silicon rectifier. A fast-switching diode must be used to prevent excessive switching transients and large power losses.

Additional details of the circuit are that  $R_5$  limits the output current of the LM100, which drives the base of  $\rm Q_2$ .  $\rm C_3$  causes the full output ripple to be delivered to the feedback terminal of the regulator. The bypass capacitor,  $\rm C_1$ , is used on the input line both to minimize the voltage transients on this line and to reduce power losses in the line resistance.

A far more complete description of switching regulators is given in Reference 7.

#### CONCLUSIONS

A regulated power supply is required in practically every piece of electronic equipment. A monolithic integrated circuit was described here which covers an extremely wide voltage range and can supply virtually unlimited power by the addition of external transistors. As indicated in Table 1, its performance is more than adequate for the majority of applications. It is flexible enough to be used as either a linear dissipating regulator or as a high efficiency switching regulator without sacrificing performance in either application. The LM100 also has fast transient response in that overshoot and recovery time can be made vanishingly small in most applications. In addition, the frequency stability is indicated by the fact that it is virtually impossible to make the regulator oscillate in a properly designed circuit.

The suitability of the design to monolithic construction is demonstrated by the fact that it is built on a 38-mil-square silicon die — a size comparable to modern silicon transistors. This small size helps to achieve high yields which are necessary to realize low manufacturing costs and insure off-the-shelf availability.

#### REFERENCES

- H. C. Lin, T. B. Tan, G. Y. Chang, B. Van der Leest and N. Formigoni, "Lateral Complementary Transistor Structure for the Simultaneous Fabrication of Functional Blocks," Proc. IEEE, Vol. 52, No. 12, pp. 1491-1495, Dec. 1964.

- G. E. Moore, "Semiconductor Integrated Circuits," Chap. V, Microelectronics, Edward Keonjian, ed., McGraw Hill, Inc., New York, 1963.

- R. J. Widlar, "Some Circuit Design Techniques for Linear Integrated Circuits," IEEE Trans on Circuit Theory, Vol. CT-12, No. 4, pp. 586-590, Dec. 1965.

- Leslie Solomon, "Ferrite Beads," Electronics World, pp. 42-43, October, 1966.

- R. J. Widlar, "The Operation and Use of a Fast Integrated Circuit Comparator," Fairchild Semiconductor APP-116, February, 1966.

- R. J. Widlar, "An Exact Expression for the Thermal Variation of the Emitter Base Voltage of Bi-Polar Transistors," Proc. IEEE, Vol. 55, No. 1, pp. 96-97, Jan. 1967.

- R. J. Widlar, "Designing Switching Regulators," National Semiconductor AN-2, April, 1967.

TABLE 1. Typical Performance of the National LM100 Voltage Regulator

| PARAMETER                         | CONDITIONS                                                      | VALUE     |

|-----------------------------------|-----------------------------------------------------------------|-----------|

| Input Voltage Range               |                                                                 | 8.5 — 40V |

| Output Voltage Range              | ,                                                               | 2.030V    |

| Output-Input Voltage Differential |                                                                 | 3.0 -30V  |

| Load Regulation                   | $R_{SC} = 0$ , $I_0 < 15 \text{ mA}$                            | 0.1%      |

| Line Regulation                   |                                                                 | 0.05%/V   |

| Temperature Stability             | $-55^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ + 125 $^{\circ}$ C | 0.3%      |

| Output Noise Voltage              |                                                                 | 0.005%    |

| Long Term Stability               | ·                                                               | 0.1%      |

| Standby Current Drain             |                                                                 | 1 mA      |

| Minimum Load Current              |                                                                 | 1.5 mA    |

DESIGNING SWITCHING REGULATORS

#### **DESIGNING SWITCHING REGULATORS**

#### INTRODUCTION

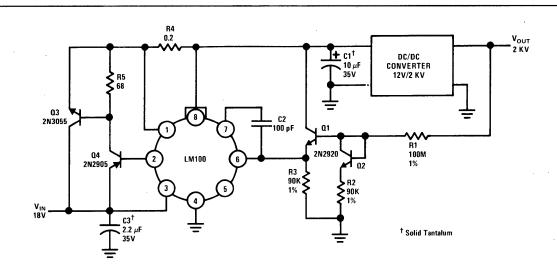

The series pass element in a conventional series regulator operates as a variable resistance which drops an unregulated input voltage down to a fixed output voltage. This element, usually a transistor, must be able to dissipate the voltage difference between the input and output at the load current. The power generated can become excessive, particularly when the input voltage is not well regulated and the difference between the input and output voltages is large.

Switching regulators, on the other hand, are capable of high efficiency operation even with large differences between the input and output voltages. The efficiency is, in fact, negligibly affected by the voltage difference since this type of regulator acts as a continuously-variable power converter.

Switching regulators are, therefore, useful in battery-powered equipment where the required output voltage is considerably lower than the battery voltage. An example of this is a missile with a 30V battery as its only power source, containing a large number of integrated logic circuits which require a 5V supply. Switching regulators are also useful in space vehicles where conservation of power is extremely important. In addition, they are frequently the most economical solution in commercial and industrial applications where the increased efficiency reduces the cost of the seriespass transistors and simplifies heat sinking.

One of the disadvantages of switching regulators is that they are more complex than linear regulators, but this is often a substitution of electrical complexity for the thermal and mechanical complexity of high power linear regulators. Another disadvantage is higher output ripple. However, this can be held to a minimum (about 10 mV) and it is at a high enough frequency so that it can be easily filtered out. Another limitation is that the response to load transients is not always as fast as with linear regulators, but this can be largely overcome by proper design. The rejection of line transients, however, is every bit as good if not better than linear regulators. Lastly, switching regulators throw current transients back into the unregulated supply which are somewhat larger than the maximum load current. These, in some cases, can be troublesome unless adequate filtering is used.

This article will demonstrate the use of a monolithic voltage regulator in a number of switching regulator applications. These include both self-oscillating and synchronously driven regulators in the 0.1A to 5A range. Circuits are shown for both positive and negative regulators with output voltages in the 2V to 30V range. Methods of isolating the integrated circuit from the input voltage are given, permitting input voltages in excess of 100V. Further, current limiting schemes which keep peak currents and dissipation well within safe limits for both over-load and short-circuit conditions are presented. Finally, component selection details peculiar to switching regulators are covered.

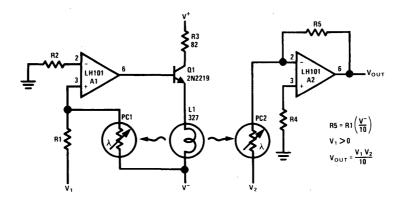

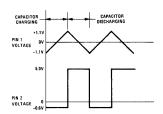

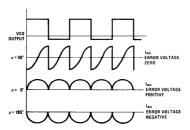

#### SWITCHING REGULATOR OPERATION

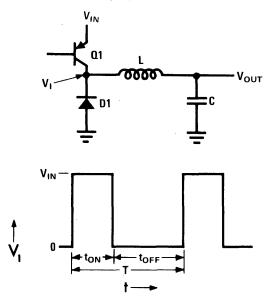

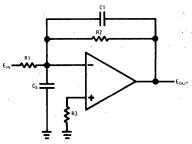

The method by which a switching regulator produces a voltage conversion with high efficiency can be explained with the aid of Figure 1.  $\mathbf{Q}_1$  is a switch transistor which is turned on and off by a pulse waveform with a given duty cycle, and  $\mathbf{D}_1$  is a catch diode which provides a continuous path for the inductor current when  $\mathbf{Q}_1$  turns off. The voltage waveform on the collector of  $\mathbf{Q}_1$  will be as shown in the figure. The output of the LC filter will be the average value of the switched waveform,  $V_1$ . If the voltage drops across the transistor and diode are neglected, the output voltage will be

$$V_{OUT} = V_{IN} \frac{t_{on}}{T}; \tag{1}$$

and it is independent of the load current. It is obvious from the equation that changes in input voltage can be compensated for by varying the duty cycle of the switched waveform. This is what is done in a switching regulator.

FIGURE 1

Switching Circuit for Voltage Conversion

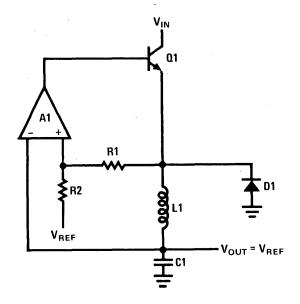

Figure 2 shows a self-oscillating switching regulator which produces this duty-cycle control. A reference voltage,  $V_{ref}$  equal to the desired output voltage, is supplied to one input of an operational amplifier,  $A_1$ . The operational amplifier, in turn, drives the switch transistor. The resistive divider, arranged such that  $R_1 \!\!>\!\!> R_2$ , provides a slight amount of positive feedback at high frequencies to make the circuit oscillate. At lower frequencies where the attenuation of the LC filter is less than the attenuation of the resistive divider, there is net negative feedback to the inverting input of the operational amplifier.

FIGURE 2 Self-oscillating Switching Regulator

In operation, when the circuit is first turned on, the output voltage is less than the reference voltage so the switch transistor is turned on. When this happens, current flow through R<sub>1</sub> raises the voltage on the non-inverting input of the operational amplifier slightly above the reference voltage. The circuit will remain switched on until the output rises to this voltage. The amplifier now goes into the active region, causing the switch to turn off. At this point, the reference voltage seen by the amplifier is lowered by feedback through R1, and the circuit will stay off until the output voltage drops to this lower voltage. Hence, the output voltage oscillates about the reference voltage. The amplitude of this oscillation (or the output ripple) is nearly equal to the voltage fed back through R<sub>1</sub> to R<sub>2</sub> and can be made quite small.

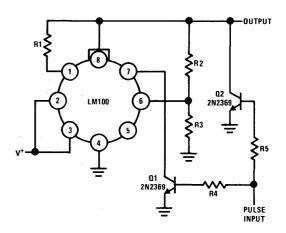

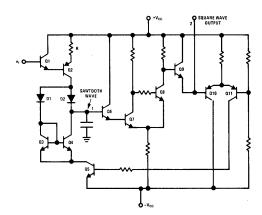

#### **THE LM100**

The switching regulator circuits described here use the LM100 integrated voltage regulator as the control element. This device contains, on a single silicon chip, the voltage reference, the operational amplifier and the circuitry for driving a PNP switch transistor. Discrete switch transistors, catch diodes and reactive elements are employed since these components are not easily integrated.

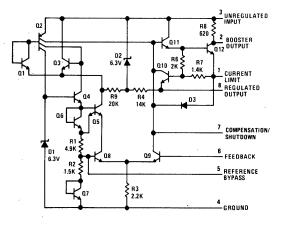

A complete circuit description of the LM100 is given in Application Note AN-1 along with a number of its applications as a linear regulator. However, a brief description will be included here in order to facilitate understanding of the regulator circuits which follow.

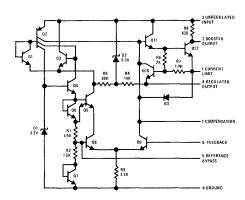

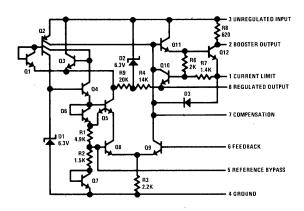

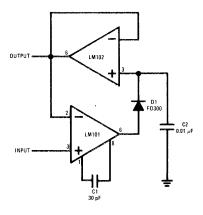

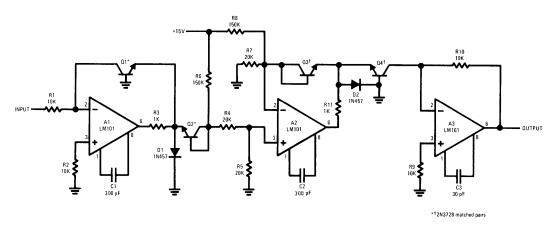

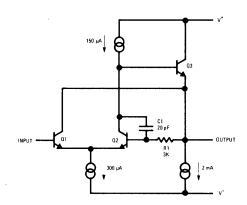

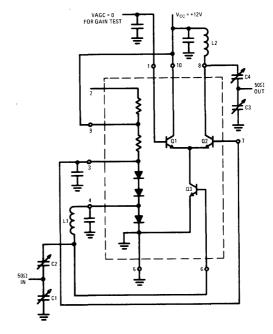

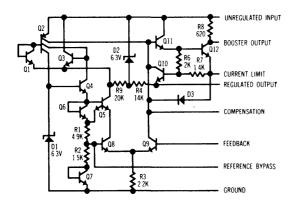

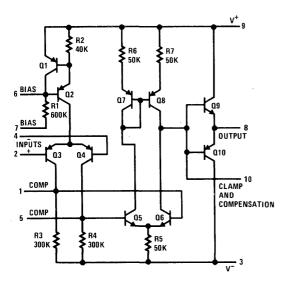

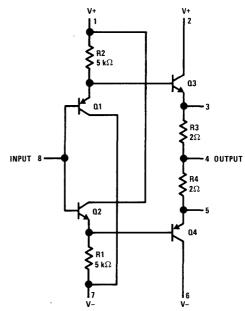

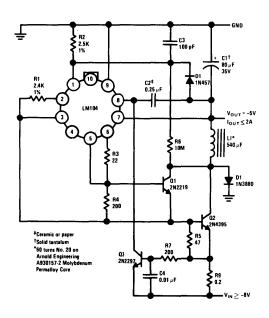

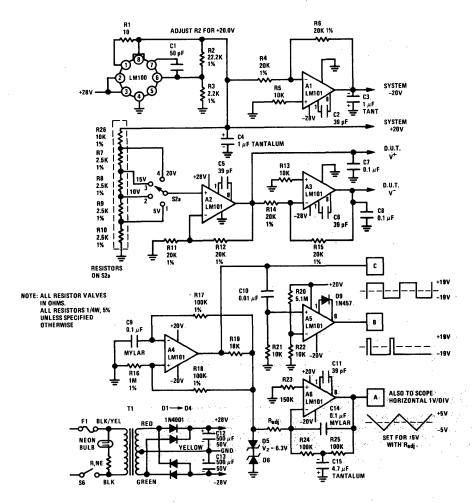

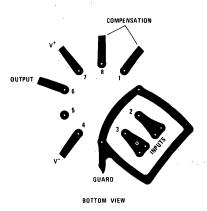

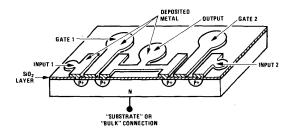

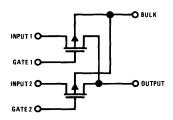

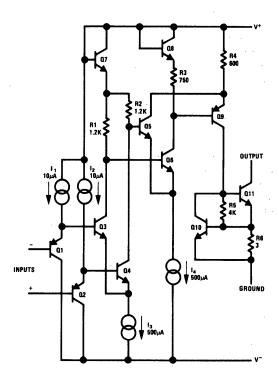

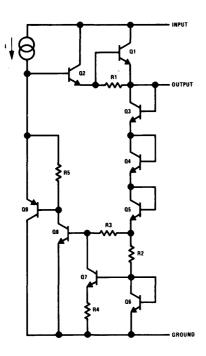

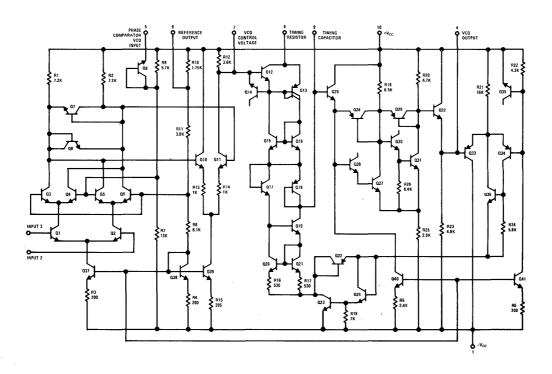

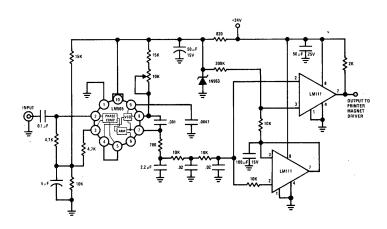

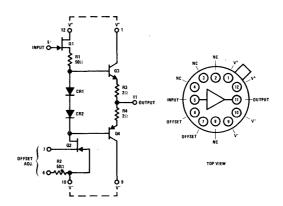

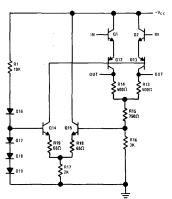

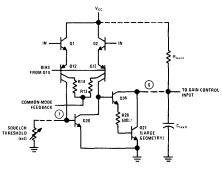

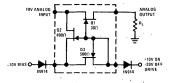

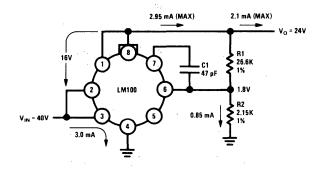

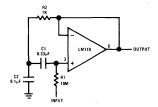

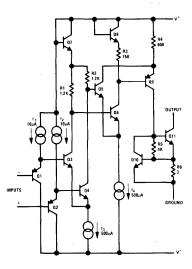

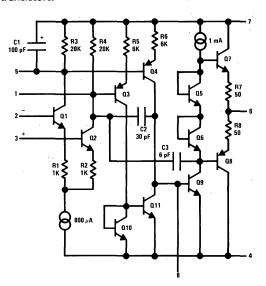

Figure 3 shows a schematic diagram of the LM100. The voltage reference portion of the circuit starts with a breakdown diode,  $D_1$ , which is supplied by a current source from the unregulated input (one of the collectors of  $\Omega_2$ ). The output of the reference diode, which has a positive temperature coefficient of 2.4 mV/ $^{\circ}$ C, is buffered by an emitter follower,  $\Omega_4$ , which increases the temperature coefficient to +4.7 mV/ $^{\circ}$ C. This is further increased to 7 mV/ $^{\circ}$ C by the diode-connected transistor,  $\Omega_6$ . A resistor divider reduces this voltage as well as the temperature coefficient to exactly compensate for the negative temperature coefficient of  $\Omega_7$ , producing a temperature-compensated output of 1.8V.

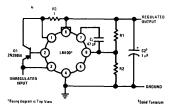

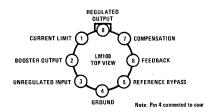

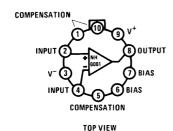

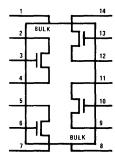

FIGURE 3

Schematic and Connection Diagrams of the LM100 Voltage Regulator

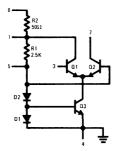

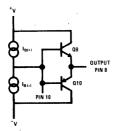

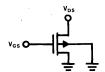

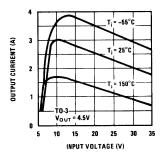

The transistor pair,  $Q_8$  and  $Q_9$ , form the input stage of the operational amplifier. The gain of the stage is made high by the use of a current source, one of the collectors of  $Q_2$ , as a collector load. The output of this stage drives a compound emitter follower,  $Q_{11}$  and  $Q_{12}$ . The output of  $Q_{12}$  is taken across  $Q_{12}$  is the part of transistor. An additional transistor,  $Q_{10}$ , is used to limit the

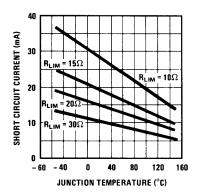

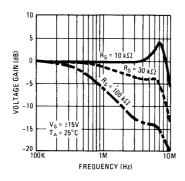

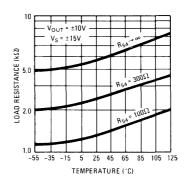

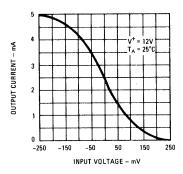

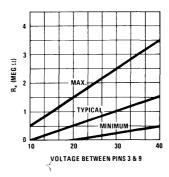

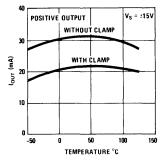

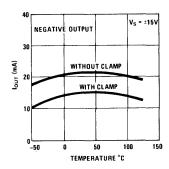

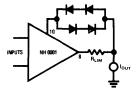

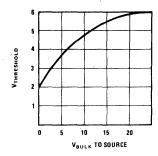

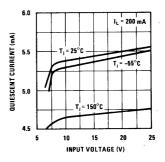

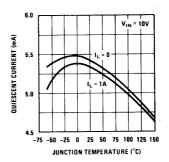

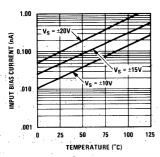

output current of  $Q_{12}$  to the value required for driving a PNP transistor connected on the booster output. This current is determined by a resistor placed between the current limit and regulated output terminals. The value of the drive current can be determined from Figure 4 which plots the output current as a function of temperature for various current limit resistors.

FIGURE 4

Switched Output Current as a Function of Temperature for Various Values of Current Limit Resistors

As for the remaining details of the circuit,  $Q_5$ ,  $Q_3$  and  $Q_1$  are part of a bias stabilization circuit for  $Q_2$  to set its collector currents at the desired value.  $R_9$ ,  $R_4$  and  $D_2$  serve the sole function of starting the regulator. Lastly,  $D_3$  is a clamp diode which keeps  $Q_9$  from saturating when it is switching.

#### **SWITCHING REGULATOR CIRCUITS**

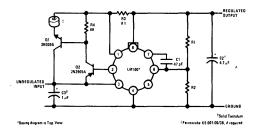

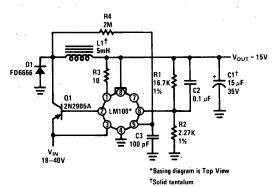

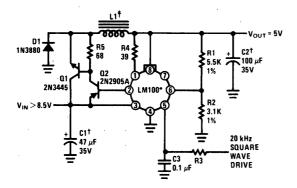

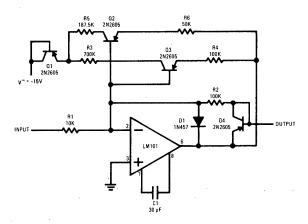

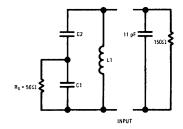

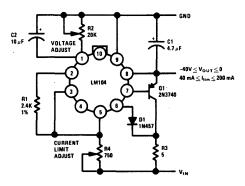

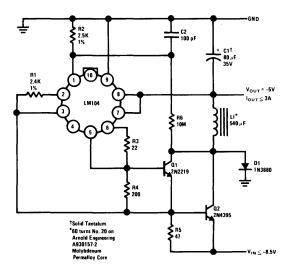

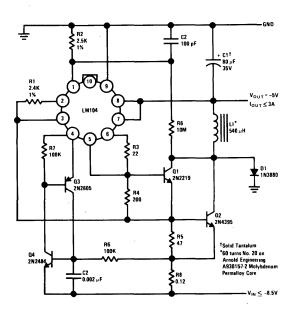

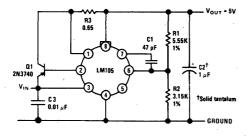

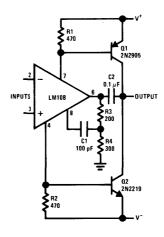

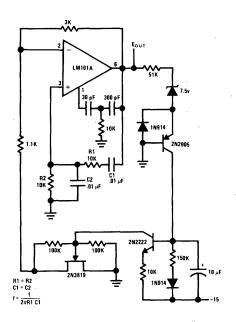

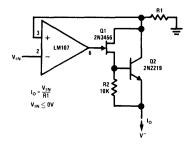

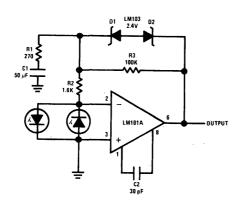

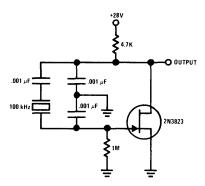

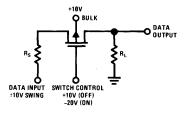

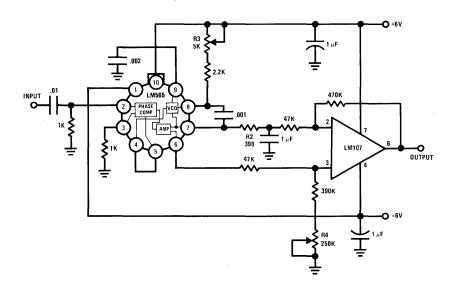

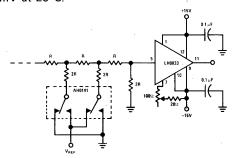

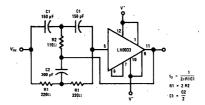

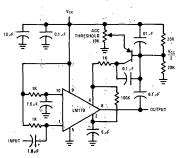

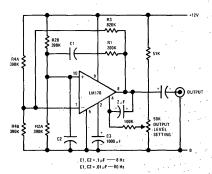

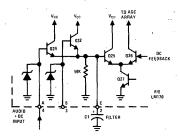

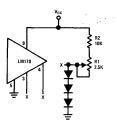

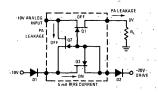

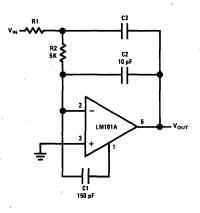

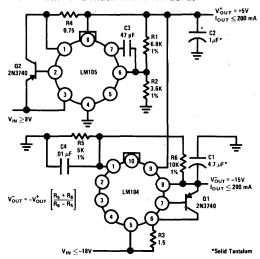

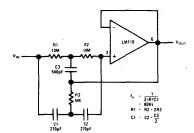

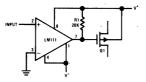

Figure 5 demonstrates the use of the LM100 as a switching regulator. Feedback to the inverting input of the operational amplifier (Pin 6 of the LM100) is obtained through a resistive divider which can be used to set the output voltage anywhere in the 2-30V range.  $R_3$  determines the base drive for the switch transistor,  $Q_1$ , providing enough drive to saturate it with maximum load current.  $R_4$  works into the 1 k $\Omega$  impedance at the reference terminal, producing the positive feedback. C2 serves to minimize output ripple by causing the full ripple to appear on the feedback terminal. The remaining capacitor, C3, removes the fast-risetime transients which would otherwise be coupled into Pin 5 through the shunt capacitance of R<sub>4</sub>. It must be made small enough so that it does not seriously integrate the waveform at this point.

The circuit shown in Figure 5 is suitable for output currents as high as 500 mA. This limit is set by the output current available from the LM100 to saturate the switch transistor,  $Q_1$ . For lower currents, the value of  $R_3$  should be increased so that the base of  $Q_1$  is not driven unnecessarily hard.

†125 turns =22 on Arnold Engineering A262123-2 molybdenum permalloy core

FIGURE 5

Switching Regulator Using the LM100

The optimum switching frequency for these regulators has been determined to be between 20 kHz and 100 kHz. At lower frequencies, the core becomes unnecessarily large; and at higher frequencies, switching losses in  $\Omega_1$  and  $D_1$  become excessive. It is important, in this respect, that both  $\Omega_1$  and  $D_1$  be fast-switching devices to minimize switching losses.

The output ripple of the regulator at the switching frequency is mainly determined by  $R_4.$  It should be evident from the description of circuit operation that the peak-to-peak output ripple will be nearly equal to the peak-to-peak voltage fed back to Pin 5 of the LM100. Since the resistance looking into Pin 5 is approximately  $1000\,\Omega,$  this voltage will be

$$\Delta V_{\text{ref}} \simeq \frac{1000 \text{ V}_{\text{IN}}}{\text{R}_4}.$$

(2)

In practice, the ripple will be somewhat larger than this. When the switch transistor shuts off, the current in the inductor will be greater than the load current so the output voltage will continue to rise above the value required to shut off the regulator. An important consideration in choosing the value of the inductor is that it be large enough so that the current through it does not change drastically during the switching cycle. If it does, the switch transistor and catch diode must be able to handle

peak currents which are significantly larger than the load current. The change in inductor current can be written as

$$\Delta I_{L} \simeq \frac{V_{OUT} t_{off}}{I}$$

. (3)

In order for the peak current to be about 1.2 times the maximum load current, it is necessary that

$$L_1 = \frac{2.5 \text{ V}_{\text{OUT}} t_{\text{off}}}{I_{\text{OUT (max)}}}.$$

(4)

A value for toff can be estimated from

$$t_{off} = \frac{1}{f} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right) , \qquad (5)$$

where f is the desired switching frequency and  $V_{IN}$  is the nominal input voltage.

The size of the output capacitor can now be determined from

$$C_1 = \left(\frac{V_{IN} - V_{OUT}}{2L_1 \Delta V_{OUT}}\right) \left(\frac{V_{OUT}}{f V_{IN}}\right)^2, \tag{6}$$

where  $\Delta V_{\text{OUT}}$  is the peak-to-peak output ripple and  $V_{\text{IN}}$  is the nominal input voltage.

It now remains to determine if the component values obtained above give satisfactory loadtransient response. The overshoot of the regulator can be determined from

$$\Delta V_{OUT} = \frac{L_1 (\Delta I_L)^2}{C_1 (V_{IN} - V_{OUT})}$$

(7)

for increasing loads, and

$$\Delta V_{OUT} = \frac{L_1 (\Delta I_L)^2}{C_1 V_{OUT}}$$

(8)

for decreasing loads, where  $\Delta I_{\perp}$  is the load-current transient. The recovery time is

$$t_r = \frac{2L_1\Delta I_L}{V_{IN} - V_{OUT}} \tag{9}$$

and

$$t_r = \frac{2L_1\Delta I_L}{V_{OUT}} \tag{10}$$

for increasing and decreasing loads respectively.

In order to improve the load transient response, it is necessary to allow larger peak to average current

ratios in the switch transistor and catch diode. Reducing the value of inductance given by Equation (4) by a factor of 2 will reduce the overshoot by 4 times and halve the response time. This, of course, assumes that the output capacitance is doubled to maintain a constant switching frequency.

The above equations outline a design procedure for determining the value for  $R_4$ ,  $L_1$ , and  $C_1$ , given the switching frequency and the output ripple. These equations are not exact, but they do provide a starting point for designing a regulator to fit a given application.

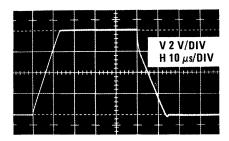

As an example, this design method will be applied to a regulator which must deliver 15V at a maximum current of 300 mA from a 28V supply. To start, a 40 kHz switching frequency will be selected along with an output ripple of 14 mV, peak-to-peak.

From (2), R<sub>4</sub> is calculated to be 2 M $\Omega$ . In determining L<sub>1</sub>, t<sub>off</sub> is found to be 11.6  $\mu$ s from (5). Inserting this into (4) gives a value of 1.45 mH for L<sub>1</sub>. The value of C<sub>1</sub> obtained from (6) is then 57.5  $\mu$ F.

In the actual circuit of Figure 5, a standard value of 47  $\mu$ F is used for C<sub>1</sub>; and L<sub>1</sub> is adjusted to 1.7 mH. The switching frequency obtained experimentally on this circuit is 60 kHz and the peak-to-peak output ripple is 20 mV. The fairly-large disagreement between the calculated and experimental values is not alarming since many simplifying assumptions were made in the derivation of the equations. They do, however, provide a convenient method of handling a large number of mutually-dependent variables to arrive at a working circuit.

More exact expressions would involve a design procedure which is too cumbersome to be of practical value.

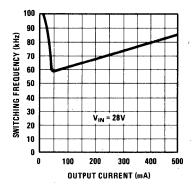

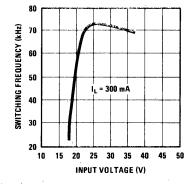

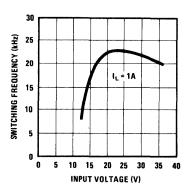

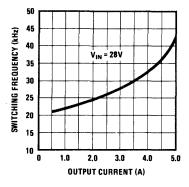

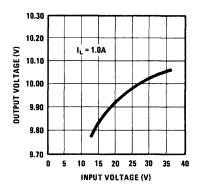

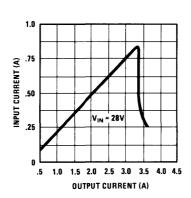

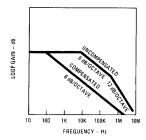

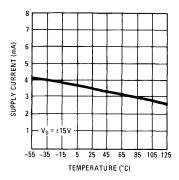

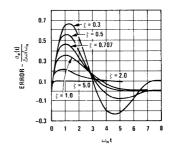

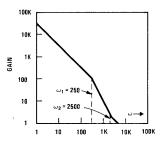

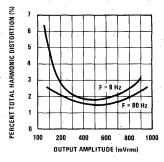

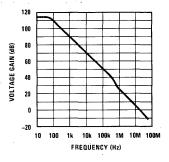

The variation of switching frequency with input voltage and load current is shown in Figures 6 and 7. The sharp rise in frequency at low output currents happens because the output transistor of the LM100  $(O_{12})$  begins to supply an appreciable portion of the load current directly.

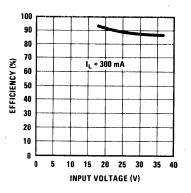

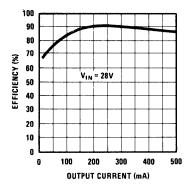

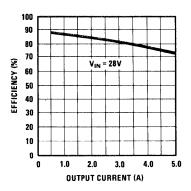

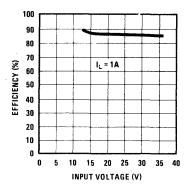

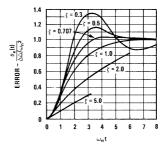

The efficiency of the regulator over a wide range of input voltages and output currents is given in Figures 8 and 9.

FIGURE 7

Switching Frequency as a Function of Output

Current

FIGURE 6

Switching Frequency as a Function of Input Voltage

FIGURE 8

Efficiency as a Function of Input Voltage

FIGURE 9

Efficiency as a Function of Output Current

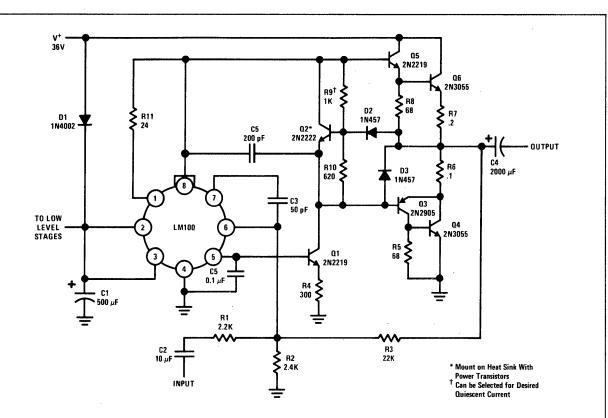

#### HIGHER CURRENT REGULATORS

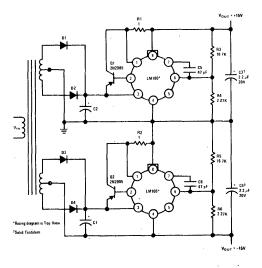

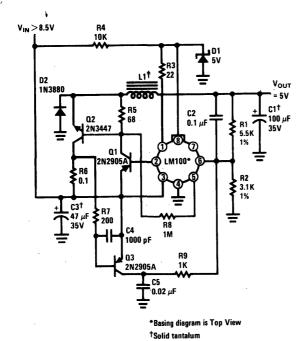

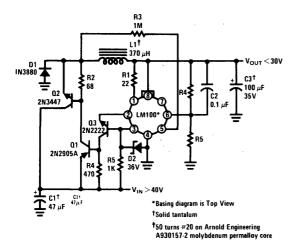

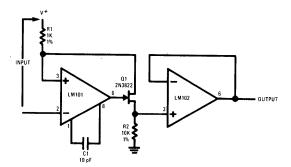

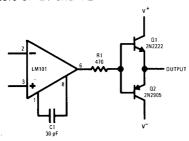

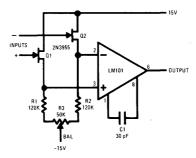

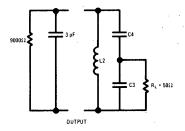

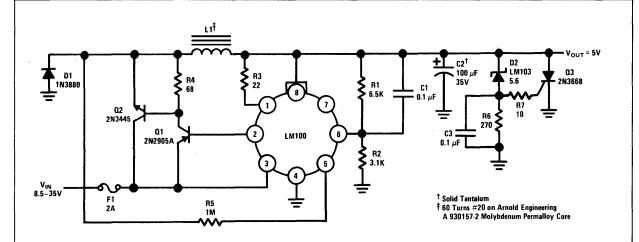

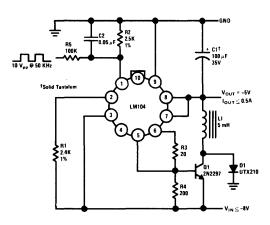

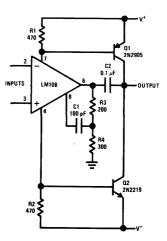

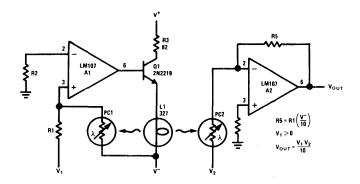

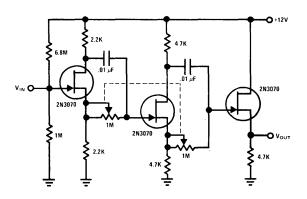

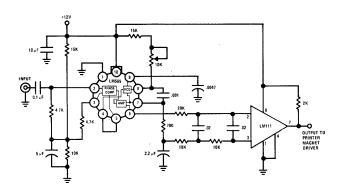

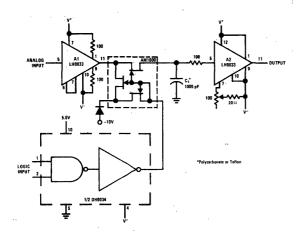

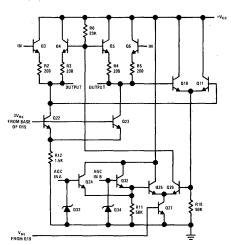

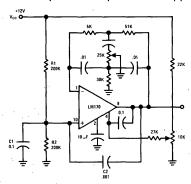

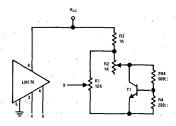

If output currents greater than about 500 mA are required, it is necessary to add another switch transistor to obtain more current gain. This is illustrated in Figure 10. With the exception of the added NPN power switch,  $Q_2$ , this circuit is the same as that described previously.

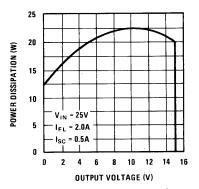

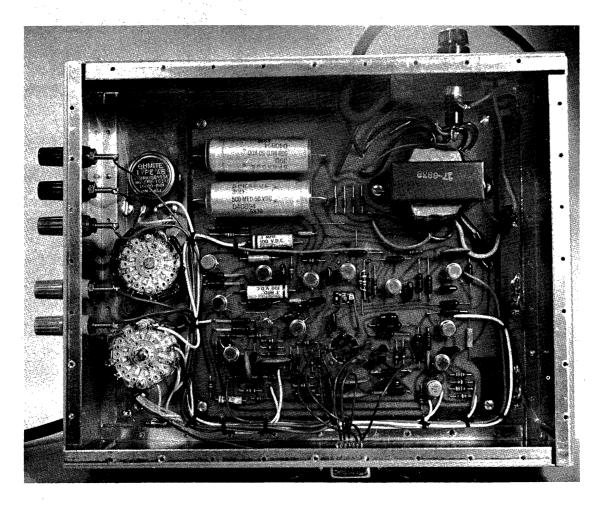

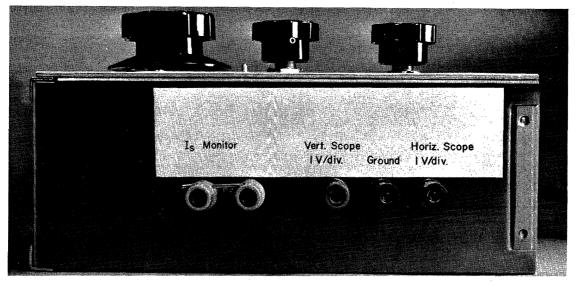

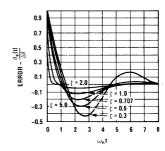

A photograph of a high-current regulator is shown in Figure 11. It is capable of delivering output currents of 3A continuously with only a small heat sink. Figure 12 shows that the efficiency is better than 80 percent at this level. Output currents to 5A can be obtained at reduced efficiency. However, the case temperature of the power switch and catch diode approach 100°C under this condition, so continuous operation is not recommended unless more heat sink is provided.

†60 turns #20 on Arnold Engineering

FIGURE 10 Switching Regulator for Higher Output Currents

FIGURE 11 High Current Switching Regulator

FIGURE 12

Efficiency as a Function of Output Current